A broadband, high efficiency, class J power amplifier (PA) design uses the relationship between drain efficiency and the ratio of drain-source capacitance to load impedance. In addition, multi-section matching is applied at the input and output to expand the bandwidth. A wideband class J PA designed with this approach and a Wolfspeed CGH40010F GaN HEMT achieved 40.0 to 41.5 dBm output power with 60 to 68 percent drain efficiency and an adjacent channel power ratio better than -30 dBc from 1.4 to 3.6 GHz.

With the rapid development of modern wireless communication technology, the amount of information transmitted is increasing and requiring wider bandwidth. This inevitably challenges the design of broadband PAs for wireless transmitters. The class J PA proposed by S.C. Cripps in 20061 uses drain-source capacitance, Cds, to control harmonics at the output of a conventional class AB power amplifier to achieve high efficiency.2 In recent years, several methods for expanding the bandwidth of class J amplifiers have been reported.3-6 Saxena et al.3 designed a continuous class J PA using the nonlinear embedding approach, achieving between 63 and 72 percent drain efficiency from 1.3 to 2.4 GHz. Friesicke et al.4 proposed a resistive-reactive class J PA with complex load impedances to explore efficiency-bandwidth tradeoffs in wideband class J designs with lossy second-harmonic loads. Andersson et al.5 described a class J PA with dynamic load modulation to obtain output power and high efficiency over a certain dynamic range, and a broadband, high efficiency PA based on hybrid continuous modes with a phase shift parameter was reported by Huang et al.6

In this article, a design method based on traditional class J PA theory, which predicts high efficiency within a certain range of Cds/RL, is described. This work analyzes the trend of drain-source capacitance with the drain-source voltage and proposes a circuit to compensate transistor output capacitance so that Cds/RL can remain in the high efficiency range. A wideband J PA was designed and fabricated to validate the approach.

ANALYSIS AND DESIGN

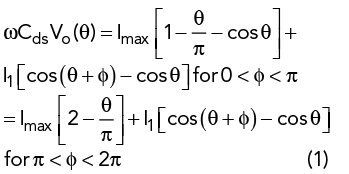

Based on traditional theory, the transistor output voltage for an ideal class J PA can be expressed as4

where Imax is the maximum output current of the drain, I1 is the output fundamental current, φ is the conduction angle, Cds is the transistor drain-source capacitance and θ is a simple representation of the matching circuit phase, its value is determined by the parameters of each part of the output matching circuit.

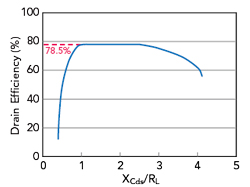

Figure 1 Drain efficiency vs. XCds/RL.

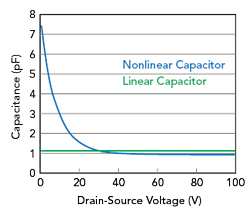

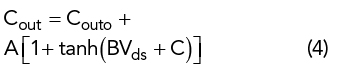

Figure 2 Output capacitance variation vs. drain-source voltage.

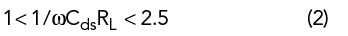

The relationship between drain efficiency and XCds/RL is shown in Figure 1 under ideal conditions,1 showing the drain efficiency remains at the ideal 78.5 percent when the value of XCds/RL is between 1 and 2.5:

This range provides additional space for the design of a broadband, high efficiency, class J PA.

Considering an ideal class B amplifier, RL can be expressed as

where Ropt is the optimal load impedance and Vdc is the drain DC bias voltage. The transistor output capacitance in pF is

where Cout is the output capacitance of transistor and Couto, A, B and C are constants associated with the transistor. For the Wolfspeed CGH40010F GaN HEMT, Couto = 0.95, A = 1192.4, B = -0.0594714 and C = -2.94696.7

According to Equation 4, the relationship between the output capacitance and the drain voltage is shown in Figure 2. When the drain-source voltage Vds is small, i.e., less than approximately 28 V, the transistor output capacitance decreases nonlinearly as the drain-source voltage increases. Beyond Vds = 28 V, the capacitance reaches a constant value of 1.185 pF.

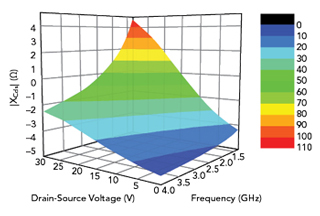

As the input signal power level has a direct impact on the magnitude of the drain signal power, changes in transistor output capacitance are discussed separately for low and high input power levels. For low input power, the effect of drain AC signal power can be ignored compared to the DC bias. The output capacitance is approximately 1.185 pF for a DC bias of Vds = 28 V. If the maximum current Imax is about 1.5 A, the theoretical high efficiency frequency range of operation is 1.44 to 3.61 GHz, found by applying Equations 2 and 3, and the corresponding drain efficiency is 78.5 percent. For large input power, the drain AC signal power has an obvious impact on the DC drain bias. For Vds = 28 V, the output capacitance is nonlinear. The relationship between the capacitive reactance, XCds, and drain-source voltage is plotted in Figure 3, showing the capacitive reactance increases as frequency decreases and drain-source voltage increases.

Figure 3 Output capacitive reactance variation vs. drain-source voltage and frequency.

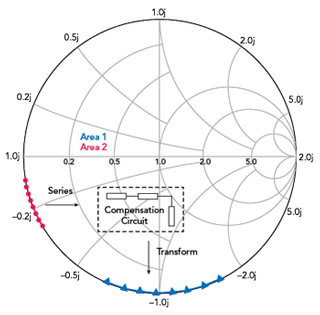

Figure 4 Impedance transformation of XCds to compensate for the nonlinear change in capacitance.