The increasing importance of spectral efficiency in mobile communication services, such as wideband code division multiple access (WCDMA) and orthogonal frequency division multiplexing (OFDM), has resulted in a fluctuating signal envelope.

The large peak-to-average power ratio (PAPR) of these modulations requires base station power amplifiers to have a high linearity. The conventional feed-forward linear power amplifier (FFLPA) has been widely utilized due to its excellent linearity performance in spite of poor power efficiency. In order to overcome this poor efficiency, digital baseband predistortion (PD) has been successfully demonstrated due to the recent advances in digital signal processors.1 Moreover, a Doherty power amplifier (DPA), along with a PAPR reduction technique, can be applied to these linearization systems to maximize the power efficiency. It is therefore desirable to compare the performance of a Doherty PD (DPD) with a Doherty FFLPA (DFFLPA) with respect to efficiency and adjacent channel leakage ratio (ACLR). It is also valuable to show the enhanced power efficiency performance of both systems when using crest factor reduction (CFR).

In this article, the measured efficiencies of power amplifiers, using the DPD technique, DPD with CFR, DFFLPA and DFFLPA with CFR, are presented. Two-carrier WCDMA signals were generated with PAPRs of 5.5, 6.5 and 9.8 dB.

The power efficiency is compared at a fixed ACLR on all systems using a 300 W peak-envelope-power (PEP) Doherty amplifier.

Overview of the Linearization Systems

The block diagram of the well-known DPD system with an embedded CFR technique is shown in Figure 1.

The baseband digital complex input signal is passed through the CFR block so as to reduce the signal’s PAPR. This PAPR suppressed signal is digitally predistorted in order to pre-compensate for nonlinear distortions of the DPA. The feedback path is required to extract the predistortion parameters and adapt these parameters for variations in temperature, aging and voltage changes.

Figure 2 illustrates a conventional feed-forward system using the DPA with CFR. The PAPR reduced signal is split into two branches. The upper branch drives the DPA and the lower branch is the reference for extracting distortions, the so-called error signal. This error signal is amplitude-controlled, phase-shifted, amplified by the error power amplifier (EPA) and finally combined with the main DPA signal so as to eliminate any distortions. The CFR block in both figures is based on generating peak cancellation pulses.

Crest Factor Reduction

The block diagram of the applied PAPR reduction architecture is shown in Figure 3. The clipper output, cn, can be expressed as A/|xn| if |xn| > A or 1 if |xn| ≤ A, where A is the clipping threshold level and the peak cancellation pulse pn is defined as

pn = xn – xncn (1)

Therefore, the PAPR suppressed signal zn is described by

Zn = xn–d – pn*hn (2)

where xn–d, * and hn denote the delayed input signal, the convolution operator and the impulse response of the low pass filter (LPF), respectively.

For multi-carrier WCDMA applications, the peak cancellation pulse should be frequency translated to the baseband, filtered, frequency translated back and combined.

This is because out-of-band emissions are residing between the different carriers and cannot be filtered out by a single low pass filter (LPF), as opposed to the single carrier application, which employs only one finite impulse response (FIR) filter.

In order to reach the targeted PAPR, an iterative method has been proposed that requires several stages.2 Therefore, a scaling factor, α, is applied after the noise shaper so as to reduce the number of stages required. α can be determined using max (|pn|)/max (|pfn|).3

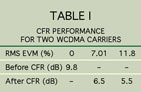

Table 1 summarizes the compression effects of the CFR technique with respect to various allowable error vector magnitudes (EVM) using two carriers of a WCDMA Test Model 1 (TM1). It should be mentioned that the ACLR was fixed to less than –45 dBc.

Experimental Results

Two carriers of a WCDMA TM1 signal with 64 dedicated physical channels (DPCH) are used in the measurements. The average 30 W DFFLPA has been demonstrated to increase the power efficiency by 2.2 percent compared to the conventional class AB FFLPA.4 In addition, a linearity optimized DPA has been demonstrated with an improved ACLR.5 The test bench for the DPD consists of a personal computer for digital signal processing (DSP), an electronic signal generator (Agilent E4438C), a 300 W PEP DPA and a vector signal analyzer (Agilent VSA89641A) for capturing the feedback signals.

The predistortion algorithm applied here is based on a memory polynomial architecture (fifth order and three memory terms) using indirect learning.6 The CFR is processed in the personal computer (MATLAB) in order to generate different PAPRs, namely, 9.8 (no CFR), 6.5 and 5.5 dB. As for the DFFLPA, it has 60 dB of gain at 2140 MHz. Figure 4 shows the measured results of ACLR, output power and efficiency for a 9.8 dB PAPR input signal. At an ACLR of –45 dBc, the efficiency is improved to 24.5 percent using PD. A 10 W power consumption for the DSP-based memory polynomial implementation7 is included.

The DFFLPA achieved an efficiency of 17 percent for the same ACLR value of –45 dBc. If the ACLR specification were set at –55 dBc, then the DPD and DFFLPA would have efficiencies of approximately 15 and 12 percent, respectively.

In Figure 5, for an input signal with a 6.5 dB PAPR (7.01 percent of EVM), the DPD and DFFLPA achieved an efficiency of 27 and 19.5 percent, respectively, at an ACLR of –45 dBc.

An important result shows that, for an ACLR specification of –55 dBc, the efficiencies are almost identical for the DPD and DFFLPA.

As seen in Figure 6, as the PAPR is further reduced to 5.5 dB (11.8 percent of EVM), the DPD’s efficiency can approach 29 percent, while the DFFLPA can achieve 21 percent.

Once again the efficiencies between the two systems are almost identical for an ACLR specification of –55 dBc. The measured results demonstrate that the DPD required more back-off than the DFFLPA as the PAPR of the input signal decreased.

This implies that the DFFLPA with CFR can be used to achieve a higher output power than the DPD with CFR, using the same LDMOS output device. Ultimately, this results in a lower cost for the DFFLPA in comparison to the DPD.

Discussion

The Doherty feed-forward linear power amplifier with CFR (5.5 dB PAPR) has achieved an approximately 20 percent power efficiency with –50 dBc of ACLR at 5 MHz offset, using two WCDMA carriers. This result is over twice that of a conventional feed-forward linear power amplifier, which is approximately 8 percent. The measured results demonstrate that the DPD required more back-off than the DFFLPA as the PAPR of the input signal decreased. This also means that the peak power of the main amplifier can be reduced to enhance efficiency with the same performance. In other words, lower peak power LDMOS devices can be used, which implies cost reduction and efficiency enhancement. According to the measurement results, the DPD performance in terms of ACLR showed a performance a little bit worse than for the DFFLPA. There are two possible reasons for this degradation. First, IQ imbalances and DC offsets were not fully optimized for digital predistortion. These impairments could limit the optimum performance for digital predistortion. Second, the test bench for digital predistortion has an approximately 40 MHz bandwidth limitation. This may be the cause of the DPD performance, when two WCDMA carriers with 5 MHz spacing were applied. One additional point is that a 10 W power consumption (CFR and DPD) for baseband processing was included in the DPD, shown in the figures as a solid line with filled square markers. No additional power consumption (CFR) for baseband processing was included in the DFFLPA, as shown by the solid line with asterisk markers. This has a 2 percent effect on the efficiency.

Conclusion

This article presents a performance comparison between the DPD and DFFLPA techniques when crest factor reduction is used. The results show that, at a lower ACLR specification of –45 dBc, the DPD with CFR can achieve up to 29 percent power efficiency, while the DFFLPA with CFR could obtain 21 percent. However, as the ACLR specification becomes more stringent, the efficiency gap between the two systems decreases. The DFFLPA system was always able to obtain a higher output power than the DPD approach, which ultimately factors into the cost.

Acknowledgment

This work was supported by the Ministry of Information and Communication of Korea under the Support Project of the University Information Technology Research Center (ITRC) and NSERC of Canada.

References

- J.K. Cavers, “Amplifier Linearization Using a Digital Predistorter with Fast Adaptation and Low Memory Requirements,” IEEE Transactions on Vehicular Technology, Vol. 39, No. 4, November 1990, pp. 374–382.

- S.H. Leung, S.M. Ju and G.G. Bi, “Algorithm for Repeated Clipping and Filtering in Peak-to-average Power Reduction for OFDM,” IEE Electronics Letters, Vol. 38, No. 25, December 2002, pp. 1726–1727.

- W.J. Kim, K.J. Cho, S.P. Stapleton and J.H. Kim, “Doherty Feed-forward Amplifier Performance Using a Novel Crest Factor Reduction Technique,” IEEE Microwave Wireless Components Letters, accepted for future publication.

- K.J. Cho, J.H. Kim and S.P. Stapleton, “A Highly Efficient Doherty Feed-forward Linear Power Amplifier for W-CDMA Base Station Applications,” IEEE Transactions on Microwave Theory and Techniques, Vol. 53, No. 1, January 2005, pp. 292–300.

- K.J. Cho, W.J. Kim, J.H. Kim and S.P. Stapleton, “Linearity Optimization of a High Power Doherty Amplifier Based on Post-distortion Compensation,” IEEE Microwave and Wireless Components Letters, Vol. 15, No. 11, May 2005, pp. 748–750.

- L. Ding, G.T. Zhou, D.R. Morgan, Z. Ma, J.S. Kenney, J. Kim and C.R. Giardina, “A Robust Digital Baseband Predistorter Constructed Using Memory Polynomials,” IEEE Transactions on Communications, Vol. 52, No. 1, January 2004, pp. 159–165.

- M. Helaoui, S. Boumaiza, A. Ghazel and F.M. Ghannouchi, “Power and Efficiency Enhancement of 3G Multi-carrier Amplifiers Using Digital Signal Processing with Experimental Validation,” IEEE Transactions on Microwave Theory and Techniques, Vol. 54, No. 4, April 2006, pp. 1396–1404.

Wan-Jong Kim received his BS and MS degrees in radio science and engineering from Kwangwoon University, Seoul, Korea, in 1999 and 2001, respectively. He is currently working toward his PhD degree at Simon Fraser University, Burnaby, BC, Canada. His research interests include wideband digital predistortion, peak-to-average power reduction techniques and integrated RF/DSP design applications.

Wan-Jong Kim received his BS and MS degrees in radio science and engineering from Kwangwoon University, Seoul, Korea, in 1999 and 2001, respectively. He is currently working toward his PhD degree at Simon Fraser University, Burnaby, BC, Canada. His research interests include wideband digital predistortion, peak-to-average power reduction techniques and integrated RF/DSP design applications.

Kyoung-Joon Cho received his BS degree in information and communication engineering from Anyan University, Anyan, Korea, in 1998, and his MS and PhD degrees in radio science and engineering from Kwangwoon University, Seoul, Korea, in 2000 and 2004, respectively. In 2004, he joined Simon Fraser University, Burnaby, BC, Canada, as a post-doctoral fellow in the school of engineering science, where he is currently involved with RF integrated circuit (RFIC) and monolithic microwave integrated circuit (MMIC) power amplifier development. His research interests include highly efficient power amplifier designs and linearization techniques.

Kyoung-Joon Cho received his BS degree in information and communication engineering from Anyan University, Anyan, Korea, in 1998, and his MS and PhD degrees in radio science and engineering from Kwangwoon University, Seoul, Korea, in 2000 and 2004, respectively. In 2004, he joined Simon Fraser University, Burnaby, BC, Canada, as a post-doctoral fellow in the school of engineering science, where he is currently involved with RF integrated circuit (RFIC) and monolithic microwave integrated circuit (MMIC) power amplifier development. His research interests include highly efficient power amplifier designs and linearization techniques.

Shawn P. Stapleton received his BS, MS and PhD degrees in engineering from Carleton University, Ottawa, Canada, in 1982, 1984 and 1988, respectively. Since 1988, he has been a professor with the school of engineering science at Simon Fraser University, Burnaby, BC, Canada. His research interests include integrated RF/DSP applications for wireless communications, GaAs MMIC circuits and power amplifier linearization.

Shawn P. Stapleton received his BS, MS and PhD degrees in engineering from Carleton University, Ottawa, Canada, in 1982, 1984 and 1988, respectively. Since 1988, he has been a professor with the school of engineering science at Simon Fraser University, Burnaby, BC, Canada. His research interests include integrated RF/DSP applications for wireless communications, GaAs MMIC circuits and power amplifier linearization.

Jong-Heon Kim received his BS degree in electronic communication engineering from Kwangwoon University, Seoul, Korea, in 1984, his MS degree in electronic engineering from Ruhr University, Bochum, Germany, in 1990, and his PhD degree in electronic engineering from Dortmund University, Dortmund, Germany, in 1994. Since 1995, he has been a professor in the department of radio science and engineering at Kwangwoon University. He is also a research associate with Simon Fraser University, Burnaby, BC, Canada, where he is involved with digital signal processing (DSP) techniques for power amplifiers for the wireless industry. His current interests include digital linearization of power amplifiers and transmitters, smart power amplifiers and integrated RF/DSP designs.

Jong-Heon Kim received his BS degree in electronic communication engineering from Kwangwoon University, Seoul, Korea, in 1984, his MS degree in electronic engineering from Ruhr University, Bochum, Germany, in 1990, and his PhD degree in electronic engineering from Dortmund University, Dortmund, Germany, in 1994. Since 1995, he has been a professor in the department of radio science and engineering at Kwangwoon University. He is also a research associate with Simon Fraser University, Burnaby, BC, Canada, where he is involved with digital signal processing (DSP) techniques for power amplifiers for the wireless industry. His current interests include digital linearization of power amplifiers and transmitters, smart power amplifiers and integrated RF/DSP designs.