When the RF test system and the device-under-test (DUT) both have coaxial connectors, hooking them together to make a measurement is easy. However, as radio-frequency integrated circuits (RFIC) have shrunk in size, traditional coaxial connectors are no longer useful. With the multitude of RF component sizes and shapes found on the market, no single connector type fits them all. A test fixture is needed to act as an electrical and mechanical interface from the RF test system to the DUT.

RFICs are commonly marketed not as die but as packaged components. Although an essential part of the component, the package is easily overlooked, usually an after-thought to designing the die. A high performance die in an inferior package results in a mediocre performing component.

An RF package can be characterized either empty or with a die inside. Many packages cannot be directly probed, in which case a test fixture provides the solution. Test fixtures are less expensive than wafer probe stations and offer more flexibility to the RF port location. With a test fixture, the matching and bias circuitry can be located near the DUT. Yet test fixtures add parasitics to the characterization scheme such as ground loops and RF reflections at the interfaces. Since the calibration plane is not usually at the package's pads, accurate de-embedding becomes essential. This article covers RF package characterization principles using test fixtures, and will help the reader to understand the package's effect on the die, especially parasitic inductances (self, mutual and ground) and capacitances (both self and mutual).

The Basic Test Fixture

An RF test fixture has three basic components - the RF launcher (usually a coaxial connector), RF interconnecting lines leading to the DUT (usually microstrip) and a block housing for the test fixture's body. Figure 1 shows a test fixture designed for evaluating leaded packages. Also known as a split block fixture, it consists of separate end sections (A-C and C-A) and a mid-section (C-C). Each end section holds an RF launcher and an interconnecting RF line. The interconnecting lines can take any number of forms (microstrip, stripline, CPW, etc.). The width of the mid-section is sized to fit the DUT.

Each section of the test fixture can be individually characterized by its S-parameters and then cascaded for the complete in-fixture response. To do this, the S matrices are converted to ABCD matrices and multiplied in a chain fashion.1 Discontinuities at the interfaces must be considered since they generate reflections. For instance, a coaxial center pin, making pressure contact to the microstrip line at B, is prone to wear and bending. After extended use, its contact degrades, causing larger reflections from B. Also, any gap between the coaxial launcher and the fixture block at B results in a discontinuity.

Mechanically, the most useful test fixtures are designed using a modular approach. The fixture blocks hold the RF launchers and a replaceable mid-section which holds the DUT. The launchers and the blocks are reusable, while the mid-section is customized to fit the DUT. The launchers have alignment pins or bolts that run the length of the block's body. Either spring-loaded end sections or tightening the bolt secures the three sections together.

To calibrate the fixture to the C reference planes, the mid-section should be replaced with calibration standards, preferably using short-open-load-thru (SOLT) below 5 GHz and thru-reflect-line (TRL) above. The parasitics in SOLT standards are difficult to quantify above 5 GHz. The benefit of TRL is that it relies on the characteristic impedance of the line to overcome reflections at the transitions. Because TRL uses different line lengths, the width of the mid-section (C-C) must be adjustable or the mid-section replaceable. Over time, repeated use eventually wears out the calibration standards and the launchers. RF repeatability of the launchers will affect the quality of the measurement, particularly at higher frequencies.2

Qualities of a Good Test Fixture

The qualities of a good test fixture include mechanical durability, good RF performance, low cost and ease of use. Calibration should be fast and accurate. An ideal fixture would have no loss, a flat frequency response, a linear phase response, no impedance mismatches, a well-known electrical length, total isolation between ports and be free of external parasitics.3 Under such ideal conditions, calibration would not be necessary. Most test fixtures offer trade-offs between these features.

In reality, mounting the DUT into a test fixture clouds the DUT's response, requiring de-embedding of the fixture's effects. Users often compensate for the test fixture through simple means such as calibrating to the ends of the coaxial test cables, subtracting a few tenths of a decibel (dB) from the measurement, or altogether ignoring the fixture's effects.

Adhering to a few guiding principles can improve the results. In general, the RF performance of the test fixture should exceed that of the DUT. For instance, the test fixture's insertion loss should be less than the uncertainty found in the DUT's insertion loss (or gain). All along the RF path, impedance discontinuities at the fixture transitions should be minimized. The bandwidth of the fixture should be wider than that of the DUT. Wideband measurements are useful for studying harmonics, for instance. In order to test sensitive devices such as filters and low noise amplifiers, the fixture's port-to-port isolation should be high.

Characterizing the Fixture's Parasitic Effects

To characterize the test fixture, three approaches are available: create a circuit model of the combined fixture and DUT; create a circuit model of the fixture alone; or de-embed the fixture from the measurement to yield the DUT. The first method requires the DUT to be inserted during characterization. The measurements are used to create RF models of the fixture and the DUT, generating both models at the same time.4 Since the reference plane between the fixture and DUT is undefined, this approach can give misleading results. Small parasitics near the DUT-to-fixture interface can often be attributed to either the DUT or the fixture side of the reference plane, a source of uncertainty. The solution is to develop an electrical model of the fixture only, using it to de-embed the fixture from the DUT measurement. Accuracy of the final DUT data will depend on how well the model actually matches the fixture. The third method is to calibrate out the fixture. Mounting calibration standards in place of the DUT shifts the electrical reference plane to the DUT contacts, de-embedding the fixture's parasitic effects.

Types of Fixtures - R&D or Manufacturing

The manufacturing and research & development (R&D) environments call for different types of test fixtures. Manufacturing demands high throughput, quick insertion, alignment and securing. Rugged, compliant contacts are made to withstand thousands of insertions and removals. The contact area (or contactor) must be kept clean for repeated insertions and extractions. For automated loading and unloading, the manufacturing test fixture tends to be mechanically complicated, providing fast, repeatable connections with acceptable RF performance and long fixture lifetimes.

Conversely, R&D fixtures are unsophisticated and somewhat fragile since only a handful of devices are tested. They can be as simple as a PCB with soldered RF connectors to either end. In R&D testing, the quality of the measurement and definition of the reference planes are of utmost importance. Correlation and repeatability between manufacturing and R&D test fixtures is often a problem.

Fixturing for Passive Components

Passive devices tend to exhibit some loss, so the test fixture's loss must not degrade the sensitivity of the measurement. Unlike active components, passive components have no gain to overcome fixture losses. A good example of the fixture's impact on a passive component measurement is measuring a filter. The test fixture's parasitics can affect the filter's poles and zeroes, shifting its frequency band response. Excessive capacitance or inductance in the fixture easily degrades the filter's band edges, or skirts. For high reject filters, where only a small amount of signal passes through, port-to-port measurements can be corrupted by fixture leakage.

To reject out-of-band frequencies, the filter presents a highly reflective load to the test fixture port. Rather than RF tuning the fixture's port to match the filter's impedance to 50 W, attenuators (or pads) could be placed in the RF path. These should be mounted close to the DUT so that reflected signals are attenuated as soon as they reflect off the filter. Placing attenuators in-line will decrease the dynamic range of the measurement.

Fixturing for Active Components

Designing the best fixture to test an active component depends on the RF application. For instance, an amplifier can easily overcome a test fixture's loss by adding a few decibels of gain to its RF output. However, depending on the power level, high power components can generate a lot of heat. Heat can be dissipated either by providing cooling to the fixture or by pulsing the bias so that only a little heat is generated. Pulsing at a low duty cycle means the device is biased only for a short period of time, allowing it to cool. When measuring for noise figure or small capacitances (on the order of femtofarads), the DUT should be shielded from any stray fields which can impinge upon it. Such sensitive DUTs are low noise amplifiers (LNA), Schottky diodes and a transistor's junction capacitance.

Fixture mismatches to the DUT continue to exist even after calibration. The mismatches are mathematically de-embedded from the measurement, not physically removed. After calibration, they will continue to interact with the DUT, especially with reflective DUTs such as filters, LNAs and power amplifiers (PA). Embedding impedance-matching networks in the fixture can lessen reflections from highly mismatched loads. Active devices such as power amplifiers have a low output port impedance. Similarly, some diodes exhibit a negative resistance. To ensure stability, the loss of the fixture itself should be small but slightly higher than the DUT.

Calibration Standards - Coaxial vs. In-fixture

As discussed earlier, calibrating the test fixture to the DUT's pads requires in-fixture calibration standards. To appreciate the difficulties, a comparison of how in-fixture standards are physically and electrically different from coaxial standards is useful.

Coaxial standards are surrounded by ground, serving to shield the center pin. Conversely, in-fixture standards are usually on a substrate mounted in place of the DUT. Substrate elements are electrically small, which means they can be approximated as lumped elements, simplifying their characterization. At high frequency, arriving at their parasitic values is simpler than with larger coaxial standards. Substrate resistors tend to be thin-film and less than a skin-depth thick. This makes their high frequency resistance more predictable than with high frequency coaxial resistors. The S-parameters of lumped elements tend to vary smoothly with frequency. When a short approaches a wavelength long, it radiates. In-fixture standards can couple to nearby metal in the fixture. Coupling and radiation are non-systematic errors difficult to de-embed.

Developing in-fixture standards can be the most difficult part of building a test fixture. They are custom-designed and usually require many iterations to build precisely. When designing calibration standards, the properties to focus on are attenuation, characteristic impedance and parasitics (inductances and capacitances). Calibration standards should be stable over temperature and mechanically repeatable. Most importantly, their response should not change each time they are inserted.

Some general guidelines can ease the design of in-fixture standards. Common substrate materials to choose from are alumina, sapphire, silicon or GaAs. The material's dielectric properties will impact the behavior of the standard (for instance, the delay of the thru). At frequencies > 2 GHz, silicon substrates exhibit higher loss and parasitic capacitance than the other materials.

Employing a photolithographic, thin-film fabrication process yields well-defined standards. When precision is not critical, a thick-film fabrication is less expensive. After fabrication, there must be a means of verifying the standards other than the test fixture. When the standards are SOLT, a TRL-calibrated fixture can be tried to independently characterize them. A good load will have constant low SWR magnitude and a linear, broadband phase response. When creating 50  CPW load standards, two 100

CPW load standards, two 100  resistors in parallel should always be chosen over one 50

resistors in parallel should always be chosen over one 50  . This approach cuts the parasitic pad inductance in half.

. This approach cuts the parasitic pad inductance in half.

RF Transitions

RF transitions are key parts of the test fixture, converting the RF signal from one medium (coaxial, microstrip, coplanar waveguide, etc.) to another. RF transitions perform two tasks. First, an impedance transformation takes place from one characteristic impedance Z0 to another. Second, it transforms the electromagnetic fields from one transmission mode to another. Carefully designing for these two criteria assures a successful transition.

When a transition is not smooth, reflections and loss appear, caused by sudden changes either in impedance or in the line's geometry. Both disturb the electromagnetic field pattern. When designed carefully, a transition will not induce reflections. For example, transformers are a simple way to adapt from one resistance to another. Using a 3:2 transformer converts a resistance from 75 to 50  . Unfortunately, impedance transformations involve both resistance and reactance, not a simple task due to parasitic inductances and capacitances at higher frequencies. When conceptually designing transitions, the changing nature of the fields must be kept in mind as they transform from one medium to another. The input and output impedances define the end goals.

. Unfortunately, impedance transformations involve both resistance and reactance, not a simple task due to parasitic inductances and capacitances at higher frequencies. When conceptually designing transitions, the changing nature of the fields must be kept in mind as they transform from one medium to another. The input and output impedances define the end goals.

De-embedding the Fixture from the Measurement

A number of schemes are available to de-embed the fixture's effects from the measurement, namely, de-embedding the microstrip lines on the PCB. These lines can be de-embedded in one of the following ways:

Linear Phase Compensation : Adding a phase delay can compensate for the phase due to a length of transmission line. This technique assumes that the phase is linear and that the line is lossless.

Normalization : A short and a thru can be used to normalize an in-fixture measurement, as shown in Figure 2 . To find the return loss of the DUT (S11,DUT), the return loss measurement (S11M) is normalized by inserting a short in place of the DUT. The short (whose S11 = -1) gives the reflection tracking error ERF

Note that a reflection normalization does not correct for directivity (EDF) or source mismatch errors (ESF), but instead assumes they are zero. Similarly, replacing the DUT with a thru gives the transmission error ETF. Transmission normalization does not correct for factors such as the load mismatch error ELF.

In-fixture Calibration : Calibration standards are mounted one-by-one in place of the DUT and measured. When quality standards are available, this is the best choice.

Thru Line : The DUT is replaced by a thru line that connects the input and output lines on the carrier substrate. This is commonly used in scalar measurements.

Time Domain Gating : The S-parameters are transformed from the frequency domain to the time domain, then the discontinuity is bounded in time. Transforming back gives the frequency response of the discontinuity.

Procedure for Characterizing a Package

Consider a package with eight leads, as shown in Figure 3 . Six of them are routed through the package walls to bond pads inside, while the other two go to a ground paddle in the package's center. For the sake of clarity, the internal routing through the package walls is not shown. The task is to generate a high frequency equivalent-circuit model of the package.

An equivalent circuit should be first sketched, looking at the package's physical construction. Based on how the leads run through the package and its dielectric layers, the circuit may consist of resistances, capacitances (both self and mutual) and inductances (both self and mutual). Rough values for the elements of the equivalent circuit should be estimated.

Next, the RF test ports are connected to the package. The package shown has six RF ports, but a vector network analyzer (VNA) has only two ports. Even if more test ports were available, modeling all the pins at once would be too complicated.5 All combinations of pins are characterized, two at a time, using symmetry wherever possible.

Before beginning any measurements, a necessary and sufficient set of experiments should be outlined to evaluate each circuit path in the package. For instance, consider adjacent pins 1 and 2, as shown in Figure 4 . The external leads are labeled P1 and P2, while the internal wire bond pads are P1' and P2'. The first experiment is to make two-port S-parameter measurements with the internal pads P1' and P2' unconnected or open. At low frequency, the capacitance terms dominate so that the inductive circuit elements can be ignored (X). The resistors represent RF leakage through the resin dielectric of the package wall. Because no current flows, the resistors can be neglected also. For the next experiment, P1' and P2' are shorted internally with a bond wire of inductance Lbw to the ground paddle. Because the inductances are a larger part of the impedance at high frequency, the capacitors can be neglected. To isolate and identify the coupling between pins 1 and 2, two experiments are using a thru and, for a one-port S-parameter measurement, a grounded thru. The ground paddle is represented as a simple inductance Lg and capacitance Cg. Higher modeling precision may require a more complicated equivalent circuit. In all experiments, a circuit simulator helps to fit the measured data to the model's equivalent circuit values.

Creating a lumped-element equivalent circuit of the package such as the one shown is valid as long as the one-way RF path length through the package is less than a tenth of a wavelength ( /10). One way to determine the path length is by measuring the phase of the port's return loss. If the phase of the return loss (S11 or S22) is greater than 0.4

/10). One way to determine the path length is by measuring the phase of the port's return loss. If the phase of the return loss (S11 or S22) is greater than 0.4 radians (where 0.4

radians (where 0.4 = 2 (for round trip)

= 2 (for round trip)  2

2 (for a wavelength)/10), then the path length is greater than

(for a wavelength)/10), then the path length is greater than  /10 and a more complicated equivalent-circuit model is needed.6

/10 and a more complicated equivalent-circuit model is needed.6

Modeling a Package Mounted to a Carrier

The design of the carrier (its layout, board thickness, dielectric, etc.) undoubtedly affects the RF behavior of the package. Before discussing how to de-embed the carrier's effect, a few fundamental questions should be asked. Since any package must be mounted to a carrier board to use it, should not the carrier and package be modeled together? Or should a package model be developed separately, independent of the carrier style? While modeling the package separately may seem more desirable, its RF behavior will always depend on the nature of the carrier. The layout of the carrier substrate will differ from one application to another, so modeling the package as though it were floating in free space is not only unrealistic, it can give misleading results when attached to one carrier design or another. Excluding the effect of the carrier and the bonding material (either a conductive adhesive or solder) makes the package model more universal but makes deriving such a model and applying it to a design more difficult.

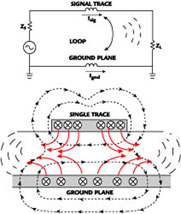

Ground Inductance

Establishing a dependable RF ground path to the die inside the package is crucial. Regular insertion and removal of the DUT into a test fixture can make repeatable grounding performance difficult. For proper current conduction, the test circuit (die, package, carrier, test fixture and test system) should form a common-mode current loop (as shown in Figure 5 ). With a single ground, the signal current Isig and ground current Ignd are equal and flow in opposite directions. The magnetic fields (dotted lines) will cancel and the electric fields (solid lines) will terminate properly.

A single ground path is rarely obtained. Instead multiple ground points occur in the circuit. This gives rise to differential mode currents, as shown in Figure 6 . Multiple grounds can cause the ground current Ignd to flow in the same direction as the signal current Isig at some points, leading to mutual coupling M and radiation.

Multiple ground paths set up ground currents traveling in different directions. Their effect shows up in the measurement as high frequency resonances and generally higher crosstalk. In particular, ground discontinuity effects will disturb sensitive RF devices such as low noise amplifiers and filters. The ground plane image current runs along the side of the conductor plating facing the substrate. The plating conforms to the contours on the surface of the substrate. This is why, at millimeter-wave frequencies, the substrate's surface roughness increasingly becomes a factor in the insertion loss.

Ground Paddle

Inside the package, the die is usually attached to a ground paddle. Similarly, the carrier often has a grounded area reserved for the package with plated-thru holes or filled vias to ground. When the bonding material penetrates into plated-thru holes, the via's inductance will change. On the other hand, gold-plated filled vias have conductive epoxy already filled in. Yet the epoxy filler has a dielectric constant different from the substrate. The frequency of operation and resulting skin depth determines the depth of penetration of the RF current into the filler, affecting its loss.

One way to measure the ground paddle's inductance is by inserting a coaxial SMA connector through the carrier and package.7 By boring a hole through the carrier and package large enough to accept a SMA center pin, it can be soldered to the ground paddle inside, as shown in Figure 7 . The connector's housing is soldered to the ground plane on back of the carrier. A simple equivalent circuit for the ground paddle is a parallel LC circuit to ground. Measuring the one-port S-parameter S11 at low frequencies, the ground inductance Lg and capacitance Cg of the paddle are

where

fr = measured resonant frequency of the parallel LgCg

Z0 = characteristic impedance (usually 50  )

)

The fixture's ground plane should closely couple to the signal path. To ensure ground integrity, map the ground path through the fixture as it travels in parallel with the signal path. The signal and ground paths should closely couple as the RF travels from the input launcher through the DUT to the output launcher. The ground path should be continuous, permitting image currents to flow unimpeded through the carrier, package and die. Indirect ground paths are what lead to ground inductance and parasitic coupling.

Conclusion

Test fixtures are often perceived as a headache, usually built as an after-thought in the design process. To deliver high performance, the RF products must be qualified using a reliable test fixture.

The size, weight and cost of RF products are driving the need for smaller and more integrated packaged components. As the market trend progresses towards smaller package sizes (< 4 mm2) and closer pad spacing (< 0.5 mm), package characterization will become even more difficult. At the same time, the drive towards lower cost makes fast and accurate package characterization essential to a design's first-pass success. Shorter product design cycles mean that the time to design and build test fixtures is getting shorter. These trends will not make the job of the test fixture designer any easier.

As the industry moves toward higher levels of component integration, the package will become more complex and require a greater number of tests. Multiple die in the same package will mean that interaction between die will go beyond the simple mutual inductance and capacitance occurring between bond wires and leads in a package.8

References

1. R. Partha, "Use Matrix Models to Make Analysis Easy for Microstrip Matching Circuits," RF Design , Vol. 20, No. 9, September 1996, pp. 50-62.

2. R. Bauer and P. Penfield, "De-embedding and Unterminating," IEEE Transactions on Microwave Theory and Techniques , Vol. 22, No. 3, March 1974, pp. 282-288.

3. Agilent Application Note AN 1287-9, "In-fixture Measurements Using Vector Network Analyzers," 1999.

4. D. Williams, "De-embedding and Unterminating Microwave Fixtures and Nonlinear Least Squares," IEEE Transactions on Microwave Theory and Techniques , Vol. 38, No. 6, June 1990, pp. 787-791.

5 A. Ferrero, F. Sanpetro and U. Pisani, "Multiport Vector Network Analyzer Calibration: A General Formulation," IEEE Transactions on Microwave Theory and Techniques , Vol. 42, No. 12, December 1994, pp. 2455-2461.

6. C.T. Tsai and W.Y. Yip, "An Experimental Technique for Full Package Inductance Matrix Characterization," IEEE Transactions on Components, Packaging and Manufacturing Technology - Part B , Vol. 19, No. 2, February 1996, pp. 338-343.

7. T. Horng, S. Wu and C. Shih, "Electrical Modeling of RFIC Packages Up to 12 GHz," IEEE Electronic Components and Technology Conference , 1999, pp. 867-872.

8. R. Gharpurey and R. Meyer, "Modeling and Analysis of Substrate Coupling in Integrated Circuits," IEEE Journal of Solid-State Circuits , Vol. 31, No. 3, March 1996, pp. 344-353.

Scott Wartenberg is a staff engineer at RF Micro Devices in Greensboro, NC. He has done RF/microwave work for Agilent Technologies, Westinghouse, Raytheon and the US Department of Defense. He earned his BS degree in electrical engineering from the University of Tennessee, and his MS and PhD degrees in electrical engineering from the Johns Hopkins University. He is the author of RF Measurements of Die and Packages (Artech House Inc., Norwood, MA 2002).