Precise device characterization is the starting point of any good circuit design. This task can be particularly challenging when the device is a high power transistor having low input and output impedances. For devices working only under pulse conditions, specific test benches exist1 but are rather complicated and usually not suitable for very high power devices.

These input and output pre-matching network circuits must be designed using a specific test fixture connected within a load-pull test bench to perform a fine tuning on both ports for power, efficiency and gain optimization. The test fixture's de-embedding is performed with the help of a vector network analyzer (VNA) usually calibrated with a classical through-reflect-line (TRL) method. The main advantage of this method is that it relies on simple transmission lines rather than a set of discrete impedance standards that are not easily available in microstrip. Such a calibration technique is not straightforward, however, and some computations must be performed for the test fixture's de-embedding.2 Moreover, this method is typically applied over a bandwidth no larger than 8:1. For wider bandwidth, a second line is employed and the band is split. A multi-line method3 can also be applied to minimize measurement errors. But these calibration techniques are rather time consuming, need care and oblige one to characterize both input and output matching networks together. This is not necessarily convenient when the transistors have rather different input and output impedance values, leading to different matching pad widths. In this last case, it would be better to characterize separately each input and output test fixture. No full model of the device can then be built, a situation not acceptable for complex MICs or MMICs design, but well suitable for high power devices. Indeed, single power transistors can come from different technologies and building a specific model for each of them is time consuming and not necessary when specific operating conditions are well defined. That is why fast and accurate characterization performed in the right conditions is highly desirable to maximize performances while saving amplifier development time and cost.

Microstrip Calibration Kit

The proposed solution consists of performing a VNA's one-port calibration with a custom 50  microstrip kit suitable for each fixture. The impedance shown by the tuned test fixture to the transistor can be measured directly by the VNA. The advantages of such a calibration are:

microstrip kit suitable for each fixture. The impedance shown by the tuned test fixture to the transistor can be measured directly by the VNA. The advantages of such a calibration are:

- it is faster and easier to perform than any TRL method

- no microstrip connections are needed during the calibration process, which tends to improve the method repeatability

- no intermediate calculations are needed for any specific test fixture de-embedding

- a broad calibrated bandwidth can be obtained without any additional standard required

- the input and output device test fixtures are characterized separately

The major problem is to realize very good microstrip calibration kits. The design of a good microstrip load is not easy.4-5 The best way to circumvent this issue is to use a coaxial broadband termination that usually provides a return loss better than 40 dB, which is about 10 dB better than any microstrip termination. A very good microstrip short can be easily realized with a thick wall at the end of the line for quasi-perfect grounding. Finally, the measurement of the microstrip open-circuit fringing capacitance can be performed efficiently with an HP 8510C using time domain reflectometry (TDR).6 The time-domain gating capabilities allow the removal of any coaxial-to-microstrip transition perturbation from the open element response for better capacitance measurement precision. The measured capacitance is modeled as a function of frequency by

C(f) = C0 + C1f + C2f2 + C3f3 (1)

Figure 1 shows the measured fringing capacitance of an open element realized with a 50  line of about 4.8 mm width on TLY5 material (

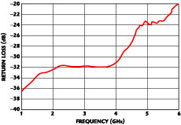

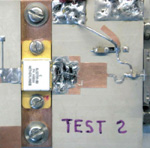

line of about 4.8 mm width on TLY5 material ( r = 2.2) having a thickness of 1.57 mm. The third-order polynomial fit gives the coefficients C0, C1, C2, C3 that are used to model the open element in the VNA. Finally, the use of a wide strip makes the design of a coaxial-to-microstrip transition not straightforward over a broad band. Figure 2 shows both a photograph and return loss of two back-to-back transitions designed (with the help of an electromagnetic simulator) to get good performances up to 4 GHz.

r = 2.2) having a thickness of 1.57 mm. The third-order polynomial fit gives the coefficients C0, C1, C2, C3 that are used to model the open element in the VNA. Finally, the use of a wide strip makes the design of a coaxial-to-microstrip transition not straightforward over a broad band. Figure 2 shows both a photograph and return loss of two back-to-back transitions designed (with the help of an electromagnetic simulator) to get good performances up to 4 GHz.

Measurements

The method's accuracy has been checked by characterizing a Philips BLS2731-50 silicon bipolar transistor working in class C under 100µs/10 percent duty cycle pulse conditions in the 2.7 to 3.1 GHz band. Compact broadband matching circuits have been realized on Rogers RT6010 Duroid material ( r = 10.2) having a 0.635 mm thickness and designed using transmission lines with Agilent's ADS. The first design was based on the impedance values given by the manufacturer. A load-pull bench using a pulsed source and mechanical tuners helped for performance improvement of one device working at a saturation level corresponding to a peak current of 4 A. This first circuit has been tuned for characterization at each frequency with a VNA calibrated with the custom microstrip kit. Figure 3 shows the set-up for the transistor characterization. The open element of the kit is connected to the tuned circuit and plugged into the VNA for direct impedance reading. The step-in-width between both open element and circuit pad does not disturb the measurement. Indeed, the open element's material is thick and has a low permittivity compared to the circuit board, thus preventing extra coupling due to some open-end effect. Moreover, the impedance measurement is done in a configuration close to one of the transistors. This can be seen in Figure 4 with the second circuit designed with the measured impedance values. Both manufacturer and measured impedance data are given for the 2.7 to 3.1 GHz band in Table 1 .

r = 10.2) having a 0.635 mm thickness and designed using transmission lines with Agilent's ADS. The first design was based on the impedance values given by the manufacturer. A load-pull bench using a pulsed source and mechanical tuners helped for performance improvement of one device working at a saturation level corresponding to a peak current of 4 A. This first circuit has been tuned for characterization at each frequency with a VNA calibrated with the custom microstrip kit. Figure 3 shows the set-up for the transistor characterization. The open element of the kit is connected to the tuned circuit and plugged into the VNA for direct impedance reading. The step-in-width between both open element and circuit pad does not disturb the measurement. Indeed, the open element's material is thick and has a low permittivity compared to the circuit board, thus preventing extra coupling due to some open-end effect. Moreover, the impedance measurement is done in a configuration close to one of the transistors. This can be seen in Figure 4 with the second circuit designed with the measured impedance values. Both manufacturer and measured impedance data are given for the 2.7 to 3.1 GHz band in Table 1 .

|

Table 1 | ||||

|

Freq. (GHz) |

Z L ( |

Philips |

Z L ( |

This Case |

|

2.7 |

9.7 |

-j1.2 |

10.8 |

-j2.65 |

|

2.9 |

6.3 |

-j2.2 |

7.4 |

-j2.25 |

|

3.1 |

4.6 |

-j4.1 |

4.8 |

-j3.4 |

Figure 5 shows the device's output power and PAE with both circuits. Our impedances allow some gain improvement at 2.9 GHz and also at 2.7 GHz where higher output power can be reached. Better efficiency is also recorded with about two percent more at this same frequency. This is not negligible with so much power at stake.

In order to check the method's accuracy, Figure 6 demonstrates a fast comparison of the transistor performances using our circuit with and without fine tuning for maximum power at the same saturation level for each frequency. Fine tuning allows rather weak performance improvement. The main change concerns the PAE evolution with input power that is different depending on the way the tuning is performed. Those results prove that the approach provides good accuracy, allowing maximum performance from the device in a broad band.

It was necessary to demonstrate that good results could also be obtained with other types of devices. For this purpose, a Mitsubishi MGF 0915A power FET transistor has been characterized in the same 2.7 to 3.1 GHz band. The quiet bias was set to 8 V/400 mA, corresponding to class B for a needed power of about 4 Wp with 200ms/10 percent pulses. Small signal parameters have been taken as a starting point for the first test fixture before optimization on the bench. Table 2 gives the measured source and load impedances as a function of frequency.

The simulations, performed with the load impedance values, showed that it is possible to synthesize a circuit with a transmission line model, allowing a theoretical output match around -22 dB in the required 400 MHz band. The output versus input power with and without output fine-tuning at three frequencies is shown in Figure 7 . The tuner helps to get only an average increased power of about 100 mWp in the band. Figure 8 shows the measured input return loss for 0.5 Wp input power without any tuning. The simulations performed using the measured source impedance values (ZS) of Table 2 show that it is very difficult to keep the input return loss below -7 dB on either side of the 2.7 to 3.1 GHz band. This correlates with the measurements and also proves the method allows a good characterization of highly mismatched devices.

Conclusion

The results shown prove that it is possible to perform fast characterization of any power device with the help of a classical load-pull bench under pulse conditions without sacrificing measurement's accuracy. The direct impedance reading on the VNA (no data computations) makes the method simple and convenient to implement to get the best performance from a power device while getting rid of any tedious modeling task.

|

Table 2 | ||||

|

Freq. (GHz) |

Z L ( |

Z L ( | ||

|

2.7 |

6.1 |

-j9.8 |

1.86 |

-j5.8 |

|

2.8 |

6.05 |

-j9.9 |

1.6 |

-j6.1 |

|

2.9 |

5.4 |

-j9.5 |

1.47 |

-j6.6 |

|

3.0 |

4.8 |

-j9.1 |

1.3 |

-j7.0 |

|

3.1 |

3.9 |

-j8.6 |

1.08 |

-j7.4 |

Acknowledgments

The author would like to thank J.P. Sipma and C. Tolant for fruitful discussions, and A. Clérambour, R. Préjant and Y.M Crêté for technical assistance.

References

1. J.P. Teyssier, M. Campovecchio, C. Sommet, J. Portilla and R. Quéré, "A Pulsed S-parameters Measurement Setup for the Nonlinear Characterization of FETs and Bipolar Transistors," 1993 European Microwave Conference Digest , Madrid, Spain, pp. 489-493.

2. J.J. Bouny, "Impedance Measurements for High Power RF Transistors Using the TRL Method," Microwave Journal , Vol. 42, No. 10, October 1999, pp. 126-134.

3. R.B. Marks, "A Multiline Method of Network Analyzer Calibration," IEEE Transactions on Microwave Theory and Techniques , Vol. 39, No. 7, July 1991, pp. 1205-1215.

4. N. Jain and D. Wells, "Design of a DC-to-90 GHz Resistive Load," IEEE Microwave and Guided Wave Letters , Vol. 9, No. 2, February 1999, pp. 69-70.

5. A.M. Khilla, "Accurate Measurement of High Power GaAs FET Terminating Impedances Improves Device Characterization," Microwave Journal , Vol. 28, No. 5, May 1985, pp. 255-263.

6. "In-fixture Measurements Using Vector Network Analyzers," Agilent Application Note 1287-9.

Pierre Bertram received his PhD degree in microwaves from the University of Paris VI, Paris, France, in 1999. His doctoral research focused on the development of a submillimeter instrument in partnership with the Jet Propulsion Laboratory, Pasadena, CA, to be launched onboard the ESA satellite Rosetta for Wirtanen comet investigations. He is currently a microwave R&D engineer with Thales, Ymare, France. His current interests concern high power transistor characterization and power amplifier design for radar purposes, as well as device reliability issues.