A high linearity Doherty power amplifier (DPA) substitutes a tunable, loaded capacitor compact microstrip resonant cell (CMRC) for the conventional λ/4 transmission line at the output of the peak amplifier. Harmonics of the peak amplifier are suppressed, while its output phase is controllable. Measured results show third-order intermodulation (IMD3) distortion of ‐50 dBc with power-added efficiency (PAE) of 47.8 percent.

The DPA is of interest for use in modern wireless communication networks to address the need for higher peak envelope power and better linearity. High efficiency is also desirable, but high efficiency with high linearity is difficult to achieve. Typical DPAs have high efficiency only at saturated output power. Efficiency is reduced at backed-off power levels to achieve the desired linearity. To improve linearity without reducing efficiency, class F and inverse class F amplifiers are employed.1 In addition, asymmetric DPAs using model-based nonlinear embedding2 and optimized asymmetrical DPAs3 have been proposed. The real frequency technique is also used,4 as well as a tunable matching network5 using a ferroelectric capacitor for improving efficiency.

In this work, a new method to improve linearity employs a loaded capacitor CMRC structure. Because the CMRC exhibits a bandstop characteristic which can be used to reject undesired frequencies, it is used in the design of fourth subharmonic mixers.6 It has also been used to improve the performance of a class F power amplifier7 and a V-Band tripler.8 For these applications, however, the CMRC is used only for harmonic suppression; phase cannot be modified easily. In this work, not only are harmonics suppressed, but phase is flexibly modified. This makes it possible to improve the linearity of the DPA without reducing efficiency.

DPA DESIGN

The architecture is shown in Figure 1. The signal of the peak (class C) amplifier passes through the CMRC and is combined with the signal from the main (class AB) amplifier at the output. The λ/4 transmission line of the conventional DPA is replaced by the loaded capacitor CMRC, which performs the appropriate impedance transformation and phase delay offset. Because the peak amplifier operates class C, the main harmonic component and AM to PM distortion are generated at its output. Unlike a conventional DPA, however, the harmonic components are suppressed, while the AM to PM phase distortion of the peak amplifier can be corrected with a modified capacitor value in the CMRC.

Figure 1 DPA using a tunable loaded capacitor CMRC.

Figure 2 Tunable loaded capacitor CMRC structure.

The tunable loaded capacitor CMRC consists of the CMRC and a loaded capacitor coupled line (see Figure 2). The CMRC is a section of microstrip transmission line with an incorporated band gap structure. Its dimensions are L = 14.2 mm, W = 4.8 mm, S2 = 0.3 mm, S1 = 0.13 mm and S3 = 2.2 mm. The loaded capacitor coupled line has a length L1 and a width W1. The slot between the coupled lines (d) is 0.4 mm. Between the coupled line and ground is a tunable capacitor. The values of L1, W1 and the loaded capacitor are listed in Table 1 for several phases in the frequency range of 2570 to 2620 MHz.

Figure 3 Simulated vs. measured |S21| and |S11| .

Simulated and measured S-parameters of the CMRC are shown in Figure 3. In the frequency range of 0.5 to 3.75 GHz, the simulated and measured insertion loss are less than 0.5 dB and the simulated and measured return loss is greater than 18 dB.

Figure 4 Tunable loaded capacitor CMRC DPA.

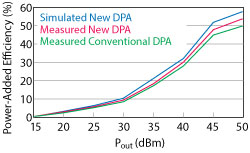

Figure 5 Power-added efficiency of the new vs. conventional DPA.

FABRICATION AND MEASUREMENT

The DPA was fabricated on a Rogers 4350 substrate with a Freescale MRF8P26080H LDMOS transistor (see Figure 4). VDS of the main and peak amplifiers was 28 V, while VGS of main amplifier was 2.65 V and the VGS of the peak amplifier was 2.28 V. The DPA was measured using a Keysight N9010A signal analyzer and E4438C vector signal generator.

Figure 6 IMD3 of the new vs. conventional DPA.

Simulated and measured PAE of the DPA using a CMRC are compared with the measured PAE of a conventional DPA in Figure 5. The maximum measured PAE of the new DPA is 54 percent at 2.6 GHz. Compared to the conventional DPA, the new DPA demonstrates an improvement of 5 to 6 percentage points. Figure 6 shows the simulated and measured IMD3 of the new DPA using a two-tone signal with a spacing of 5 MHz centered at 2.6 GHz. IMD3 is considerably improved compared to that of the conventional DPA due to the tuned loaded capacitor of the CMRC. The max IMD3 of the new DPA demonstrates an 18 dB improvement compared to a conventional DPA. Table 2 compares the performance of the new DPA design with several of the referenced works, showing that it simultaneously achieves low distortion and high PAE.

CONCLUSION

A novel, high linearity DPA uses a loaded capacitor CMRC structure to perform phase tuning and filtering. The harmonics and AM to PM distortion of the peak amplifier are suppressed, improving linearity compared to a conventional DPA, while preserving PAE.

References

- X. Yao, S. C. Jung, M. S. Kim, J. H. Van, H. Cho, S. W. Kwon, J. H. Jeong, K. H. Lim, C. S. Park and Y. Yang, “Analysis and Design of the Doherty Amplifier Based on Class F and Inverse Class F Amplifiers,” Microwave Journal, Vol. 53, No. 3, March 2010, pp. 100–103.

- H. Jang, P. Roblin, C. Quindroit, Y. Lin and R. D. Pond, “Asymmetric Doherty Power Amplifier Designed Using Model-Based Nonlinear Embedding,” IEEE Transactions on Microwave Theory and Techniques, Vol. 62, No. 12, December 2014, pp. 3436–3451.

- J. Kim, B. Fehri, S. Boumaiza and J. Wood, “Power Efficiency and Linearity Enhancement Using Optimized Asymmetrical Doherty Power Amplifier,” IEEE Transactions on Microwave Theory and Techniques, Vol. 59, No. 2, February 2011, pp. 425–434.

- G. Sun and R. H. Jansen, “Broadband Doherty Power Amplifier Via Real Frequency Technique,” IEEE Transactions on Microwave Theory and Techniques, Vol. 60, No. 1, January 2012, pp. 99–111.

- A. Tombak, “A Ferroelectric-Capacitor-Based Tunable Matching Network for Quad-Band Cellular Power Amplifier,” IEEE Transactions on Microwave Theory and Techniques, Vol. 55, No. 2, February 2007, pp. 370–375.

- Q. Xue, K. M. Shun and C. H. Chan, “Low Conversion Loss Fourth Subharmonic Mixers Incorporating CMRC for Millimeter Wave Applications,” IEEE Transactions on Microwave Theory and Techniques, Vol. 51, No. 5, May 2003, pp. 1449–1454.

- S. Chen and Q. Xue, “A Class F Power Amplifier with CMRC,” IEEE Transactions on Microwave Theory and Techniques, Vol. 21, No. 1, January 2011, pp. 31–33.

- S. Lin, P. Y. Ke, H. C. Chiu and J. S. Fu, “High Performance 0.15 μm Gate PHEMT V-Band Tripler Using Compact Microstrip Resonant Cell Technique,” TENCON 2011-2011 IEEE Region 10 Conference, November 2011, pp. 1240–1241.