Improving Accuracy and Reliability of Microwave On-wafer Silicon Device Measurements

Troels Emil Kolding

Aalborg University, RISC Group Denmark

Aalborg, Denmark

This article summarizes recent research findings and general guidelines for microwave on-wafer measurement of devices fabricated using silicon technologies. Issues specific to low resistivity substrates and low conductance metallization are detailed, and robust design and measuring techniques are suggested to enhance both reliability and accuracy of on-wafer measurements. To apply proper compensation of parasitic effects, impedance standard substrate (ISS) calibration combined with successive de-embedding is discussed, on-wafer measurements are assessed and proper measures are suggested. The effectiveness of such measures as well as various silicon-specific effects are illustrated using device and structure measurements. Finally, novel techniques are proposed that may be used to evaluate the accuracy of a given calibration/de-embedding method.

On-wafer characterization is an effective and necessary means to achieve a thorough understanding and accurate models of active and passive integrated devices. The importance of having accurate on-wafer characterization methods has recently been re-emphasized by the application of low cost silicon technologies at RF and microwave frequencies. Silicon devices are highly influenced by their extrinsic environment, and manufacturer-supplied device models are often moderately, or even poorly, accurate at gigahertz frequencies. To achieve successful first-try silicon RF circuits, the establishment of accurate test methodologies for on-wafer microwave evaluation and characterization is an important research task. However, on-wafer verification is a serious challenge due to the high substrate losses, low conductivity metallization and large tolerances typically encountered with low cost silicon processes. This article addresses issues that relate to the accuracy and reliability of on-wafer device measurements. Both issues are critical to ensure valid measurements.

The results presented here are generally applicable to all silicon processes, including low cost CMOS technology where substrate resistivity may be very low -- typically 10 O-cm. In fact, the benefit of using the proposed techniques is highest for highly doped substrates. To illustrate the full scope of applicability of the proposed methods, all measurements presented in this article have been conducted on test structures from standard CMOS processes.

SILICON MEASUREMENT CONCERNS

Most concerns with high frequency silicon device measurements are related to the metallization used, low substrate resistivity and high process tolerances. While awaiting a shift to copper technology, most silicon foundries currently utilize aluminum metallization. Aside from having a relatively low conductance, aluminum metallization suffers from instantaneous oxidation when exposed to air. Although the resulting 5 to 10 nm aluminum-oxide layer is very hard (and thus provides desirable long-term protection), it also constitutes a major problem for on-wafer probing.1 At a microscopic level, the surfaces of pads and tips are very rough, and the actual metal-to-metal spot area is somewhat smaller than the area of the tip. Small vibrations in the measuring setup will lead to short-term exposure of raw aluminum to air, which, again, results in a degradation of the contact over time. Reliable silicon measurements are generally only achieved by use of an anti-vibrant table and measures for preventing vibrations from being transferred to the probes via cables. This aspect should not be underestimated since cables are often inflexible in order to achieve low losses. In general, tungsten probe tips are very stiff and thus provide more efficient penetration of aluminum oxide than beryllium-copper (BeCu) probe tips.1 However, due to higher stiffness and the fact that tungsten is more susceptible to oxidation than BeCu, tungsten probes may be less reliable on aluminum pads if the setup is not sufficiently damped.

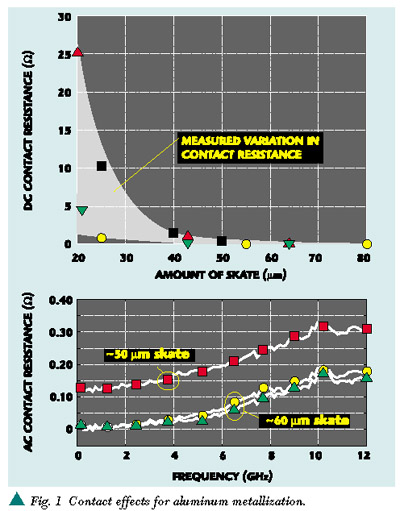

One possible but brute-force countermeasure is to use a large amount of probing skate, as shown in Figure 1 . By applying more pressure to the probes, a higher contact spot area is accomplished, which decreases the contact resistance. In addition, susceptibility toward microscopic vibrations in the setup is reduced. Practice implies that a repeatable and consistent contact is first achieved after 50 to 60 µm of skate. Note that as the skate is increased to very high values, the absolute value of the contact resistance converges to the contact resistance of the calibration chip. (Gold metallization corresponds to 0 O.) Although the contact at low skate may be stable over time, provided an antivibrant setup is used, the high resistance spread from touch-down to touch-down is of major concern. In comparison, a skate around 20 µm is sufficient for gold-based test structures.

The unfortunate drawback of using excessive skate is increased wear of the expensive microwave probes and the measuring structures located on the silicon die. Although a large skate results in a small, although not generally negligible, contact resistance at low frequencies, the data plot illustrates that the frequency dependency nevertheless makes this resistance significant for most RF and microwave characterization measurements (for example, in the measurement of high Q CMOS varactors where series device losses may easily be very small in comparison). For measurements where a change in the contact resistance on the order of a few ohms is critical, measurements should not be conducted over time intervals longer than approximately 15 to 20 minutes.

A fundamental consequence of low substrate resistivity is that both inter-terminal and inter-port (forward) coupling of typical on-wafer test fixtures become very significant. The basic origins of forward coupling are shown in Figure 2 . Aside from the direct fringing capacitance through the oxide, another and more dominant effect is caused by substrate interactions. Since quite large pads are required for the aforementioned reasons of reliability, the large pad-substrate capacitance of the probing pads brings the semiconducting substrate into play. Even for optimized RF/microwave pads, pad-substrate capacitance values on the order of 50 to 150 fF are typical. Note further that since the coupling path goes through deeper layers of the semiconducting substrate, this coupling is relatively insensitive to any surface grounding of the substrate.

For typical test fixtures (with a 100 µm gap) fabricated in several standard submicron CMOS processes, the measured forward coupling is shown in Figure 3 . Both epitaxial and bulk substrate configurations are compared. A bulk coupling configuration usually displays significantly better isolation performance due to the absence of the highly doped p+ substrate layer. The coupling is due to the low substrate resistivity and not direct fringing as is evident from the data where a case with pure fringing, is included. The better of the shown CMOS processes uses a dummy-patterned substrate with deep shallow-trench isolation. Although this type of process is superior to the other considered CMOS technologies, the absolute coupling values at high frequencies make the impact significant for many device measurements.

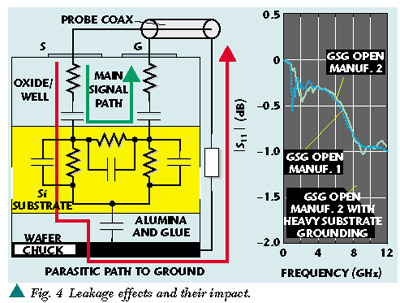

Potentially, the low substrate resistivity can also cause detrimental leakage effects that can significantly distort the measurements at even moderate radio frequencies.2 The basic mechanisms are shown in Figure 4 ; the illustrated parasitic path through the wafer, chuck and coax can give rise to a low frequency resonance (1 to 2 GHz). The problems depend highly on the particular measuring setup as seen in the example where probes from two different manufacturers are compared. To avoid this phenomenon, extensive grounding of the substrate surface is necessary. (A Teflon spacer may reduce effects but is not a viable long-term solution.) A particular measuring system may be tested by fabricating an on-wafer open standard with no substrate grounding. If the measured input reflection looks similar to the ones plotted in the example, preventive measures in terms of additional substrate grounding are required.

However, a potential drawback of using extensive substrate grounding is that in some cases the behavior of the device under test (DUT) may be affected. Hence, inaccuracies may occur since the DUT is not measured in a realistic environment that resembles the application in a real circuit. An example that illustrates this condition is shown in Figure 5 . The two curves represent two identical transistors measured in two different test fixtures. For one test fixture, only the substrate taps of the transistor have been connected to ground. For the other example, a large substrate grounding has been established in conjunction with the test fixture. The test fixtures have been shielded to mitigate the possible leakage effects described previously.3 Note that the improved substrate grounding affects the device performance at higher frequencies. Such alterations may be critical to accurate device modeling and can prevent measurement realism.

The effects of aluminum metallization and substrate resistivity generally have a large impact on device measurements. Due to these effects, it appears impossible to create a measuring scenario where the test fixture generally has a negligible impact on device performance. Another problematic issue is that these parasitic effects are associated with large tolerances. Die-to-die variations on the order of 20 to 30 percent are not uncommon. This condition makes compensation particularly difficult and statistical measures are generally required.

RELIABILITY CONSIDERATIONS

Reliability is one of the major requirements of all measurements and represents the extent to which the measurement yields the same results in repeated trials. For on-wafer measurements, reliability refers to the probing characteristics as well as the process tolerances of the test fixture in which the device is mounted. For probing, both the probing pressure and the probe alignment must be highly consistent from measurement to measurement. For consistent overtravel and skate, it is advisable to place alignment marks on the die near the pads. In order to reduce the possible contact resistance variations, it is necessary that the pads are large enough to accommodate sufficient skate. As a minimum, the two top metal layers should be used for the pad layout to prevent the aggressive skating from becoming detrimental to the pad. If ground pads are made using all stacked metal layers in order to ground the underlying substrate, it should be determined that the possible height difference between signal and ground pads does not compromise the probing reliability. For high amounts of skate this situation appears to be of less concern,3 but care must be exercised. A visual inspection of the touch-down marks on both ground and signal pads appears to be a simple yet efficient test.

The test fixture design also has a significant impact on the overall measuring reliability. Since fixture parasitics typically display relative tolerances, they should be kept small to reduce overall measuring tolerances. However, since most silicon processes display significant process variations, good design practice is not always sufficient to reduce the test fixture tolerances adequately. Further improvements may be achieved by exploiting the matching properties of silicon processes. Even for low cost CMOS technology, the matching of device and process parameters is fair if two components are placed near each other on one die. Hence, effects that require compensation should be estimated using test structures located near the DUT. Consequently, compensation should be performed on a die-to-die basis. All design guidelines that are normally associated with the achievement of good matching should be observed in this context.

Although the above guidelines are closely observed, the reliability of one measurement still may not reach a satisfactory value. To further improve the overall measuring reliability, random effects can be averaged over several measurements. Reliability r is often defined as the variance of the true parameter divided by the variance of the total measurement. Hence, r is a number between 0 and 1. If the reliability of a single measurement is r(1), the overall reliability after n repeated measurements becomes

Stability or robustness of the measurements is also improved by using more measurements since outliers have less effect. However, one assumption for the method is that errors are random and uncorrelated. Unless care is taken, an operator may introduce time-varying errors when re-measuring the same structure. One reason for this occurrence may be a slow degradation of the re-measured test structure. At 50 to 60 µm of skate, the lifetime of aluminum pads corresponds to relatively few touch-downs before the contact effects become nonreproducible.

ACCURACY CONSIDERATIONS

Accuracy is the other major requirement of most types of measurements. Accuracy may be defined as the extent to which the average of a large set of measurements deviates from the true value. Accuracy is always a strong function of the equipment and the extent to which the DUT performance falls within the measuring specifications. However, for on-wafer measurements, and particularly silicon technologies, the design of the test fixture and the methods chosen for compensation also require thorough consideration.

The test fixture holding the DUT should be characterized by a few dominating effects/parasitics for lowest compensation complexity and highest accuracy. However, fixture parasitics must be low in order to increase the dynamic range of the measurement. A trade-off between the two is usually required in practice. Here it is very important to consider each individual measuring scenario and the DUT properties. In order to simultaneously reduce parallel parasitics and facilitate good probing reproducibility, it appears to be a fair trade-off to use pad dimensions on the order of 70 to 80 µm. To mitigate potential leakage effects it is advisable to use adequate substrate grounding near signal pads. However, since extensive grounding of the substrate may affect the behavior of the device and distort measurements, it is essential that the substrate taps are isolated somewhat from the device (unless they are in fact an actual feature or part of the DUT or its natural environment in the circuit application). Guard rings and wells may be incorporated to effectively implement such isolation.

An alternative and extremely effective measuring strategy that reduces substrate effects is to use a shield-based measuring fixture, as shown in Figure 6 .3 The shield-based test fixture provides an accurate common ground and purely capacitive input characteristics up to very high frequencies. Furthermore, the forward coupling caused by the substrate is reduced to generally negligible levels (typically below 50 dB at 18 GHz). The microstrip-like fixture allows a flexible substrate configuration and an accurate implementation of on-fixture short, open and thru standards.3

Accurate compensation of the measurement is required to address the metallization and substrate losses inherent to CMOS technology. To do so, a broad range of techniques exist. There are several reasons why many researchers view stand-alone or two-tier, on-wafer silicon calibration as being less applicable than ISS calibration combined with successive de-embedding approaches. Some of the most important reasons include the fact that high forward coupling of on-wafer, two-port standards is not addressed by common calibration approaches (although this shortcoming is relaxed with the shielded test fixture). In addition, the tolerances are high, which only renders TRL calibration applicable. One universal calibration kit is not practical, and calibration structures must be repeated on all fabricated die. This requirement results in a high cost compared to most accurate de-embedding approaches. In addition, calibration techniques are not as flexible as de-embedding techniques to address devices of various geometries and shapes. Hence, several custom-made calibration kits are required on each test wafer. Finally, calibration may not be generalized as easily to N-port measurements as de-embedding methods. Many devices, such as the RF MOSFET, may best be characterized using three-port measurements.

Consequently, a de-embedding method that is tailored to the parasitics of the test fixture appears to provide a more accurate and less expensive solution. However, for silicon-on-isolator (SOI) technology, very good results have been achieved recently with on-wafer, two-port TRL calibration.4 Unfortunately, an extensive comparison in terms of accuracy still remains to be seen between ISS calibration with de-embedding and silicon-based on-wafer calibration.

For the ISS calibration, the line-reflect-match/line-reflect-reflect-match (LRM/LRRM) technique5 appears to be very effective and accurate up to very high frequencies. This type of calibration facilitates simple automated compensation, which is very attractive in the on-wafer environment. Since load and thru standards are treated with high weight, LRM/LRRM techniques often result in a less accurate response near open and short ends of the Smith chart. Since many on-wafer devices are located in these impedance areas, this drawback is often of concern in practice. However, as de-embedding methods usually employ specific open and short standards, the accuracy of these specific areas is effectively improved.

For de-embedding, several of the aspects inherent to silicon technology require specific consideration. Although widely disputed in the literature, it is absolutely essential that the test fixture forward coupling is estimated and that proper correction is made. This requirement has been verified using physical device properties.6 An equally convincing test, shown in Figure 7 , illustrates that the presence of a dummy FET (unconnected except for substrate taps, which are grounded) does not alter the test fixture forward coupling to a measurable extent. Hence, an open test fixture provides an effective and accurate method to estimate this coupling. In addition, it is important that a de-embedding method is chosen that specifically incorporates contact effects and coupling mechanisms associated with the fixture gap. Specifically, it is critical that imperfections of the in-fixture de-embedding standards are taken into account. Failure to do so often leads to significant over-estimation of test fixture parasitics and, thus, an erroneous prediction of DUT performance.4

Accurate de-embedding may be achieved using the four-step de-embedding method, which is suited for measurements on silicon devices, works with most standard test fixtures and incorporates the previously detailed silicon-related issues.7 The model topology applied by the four-step de-embedding method is shown in Figure 8 . After fabricating simple on-wafer standards, the various components of the model may be estimated for a given test fixture. The measurements are then de-embedded using impedance and admittance matrix calculations.

VERIFICATION TECHNIQUES

With the potential pitfalls specified in this article, it is critical that some means of evaluating measurement accuracy are made available. With a high accuracy process such as a ceramic and gold-plated ISS, accurate devices can be fabricated to verify a conducted multiport calibration (for example, open stubs and other predictable test devices). However, for low cost silicon processes it is very difficult to achieve an accurate on-chip reference due to large process tolerances. Hence, other means of verification are required. Note that in general the re-measurement of in-fixture standards will only verify that the computer algorithms execute properly and that the measuring reliability is high.

When employing de-embedding techniques one of the most basic tests is to evaluate the physical nature of the extracted test fixture parasitics. With such a sanity check one may ensure that lines (although small) display a resistive and inductive component and that admittances are mainly capacitive with resistive loss. Further, different segments of the test fixture may be compared in terms of the geometry and their extracted parasitics. Provided that the chosen de-embedding method provides an accurate representation of the particular test fixture, scalability of parasitics is a good measure of accuracy. If a fixture line is twice as long as another fixture line, the lines' associated parasitics should scale in an equal manner. It should be noted that by specifically considering the contact effects of each probe, various symmetry considerations on the test fixture may be used to verify de-embedding accuracy. Extraction of the contact effects requires the use of a CMOS short standard, which must be made as ideal as possible.7 With this test it may be verified if the ISS calibration has made proper compensation for the inductive effect of the short and load standards residing on the ISS. The specific consideration of several individual effects is one of the main advantages of the four-step de-embedding method mentioned previously.

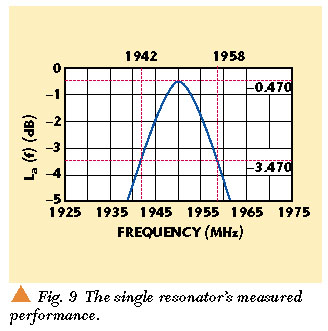

Another efficient method to test the validity of a measurement is to employ device physics to predict scaled behavior of devices and check if this is also verified through measurements.2,6 The main advantage of this method is that it reduces the concern of process tolerances. Wafer-to-wafer tolerances of silicon technologies are usually quite large in comparison to die-to-die tolerances for chips taken from the same lot. For devices that are kept closely together on the same dice, even very good matching may be observed. Hence, the prediction of absolute values is associated with great difficulty while scalability is predicted with high accuracy. One technique that exploits this basic idea is the admittance test. The admittance parameters of different-sized transistors are used and it is determined if there is a calibration offset in all parallel directions. (The validity of extracted coupling parasitics of the test fixture is checked.) The idea is that specific y parameters must scale with the device width provided the bias conditions are identical. Such a test is shown in Figure 9 .

Another test, the cutoff-frequency test, evaluates the consistency of extracted fT for different-sized devices at identical bias conditions. Any discrepancy will indicate an inaccurate estimation of test fixture series and parallel parasitics (or, potentially, an inaccurate ISS calibration). The principle of the cutoff-frequency test is also depicted in the example. However, note that all verification techniques that employ scaling characteristics call for very high consistency in the FET layout. In particular, a constant ratio between intrinsic parasitics and extrinsic parasitics (for example, connections and wiring) must be maintained. In addition, bulk effects must be closely considered for high FET scalability at microwave frequencies.

CONCLUSION

Several microwave measuring issues related to silicon devices have been described. A study of contact effects and coupling mechanisms yielded several important design and measuring guidelines for achieving accurate and reliable measurements. ISS calibration combined with silicon-minded de-embedding appears to be an accurate and flexible choice to obtain good measurement accuracy. Sanity checks and physical properties of scaled devices can be applied to verify the accuracy of a conducted ISS calibration/de-embedding method.

ACKNOWLEDGMENT

The author would like to acknowledge the helpful discussions with RISC Group colleagues Ole Kiel Jensen and Michael Bohl Jenner. *

References

1. J.L. Carbonéro, G. Morin and B. Cabon, "Comparison between Beryllium-copper and Tungsten High Frequency Air Coplanar Probes," IEEE Transactions on Microwave Theory and Techniques , Vol. 43, December 1995, pp. 27862793.

2. T.E. Kolding, "General Accuracy Considerations of Microwave On-wafer Silicon Device Measurements," IEEE MTT-S International Microwave Symposium Digest , (Boston, MA, USA), June 2000, pp. 18391842.

3. T.E. Kolding, O.K. Jensen and T. Larsen, "Ground-shielded Measuring Technique for Accurate On-wafer Characterization of RF CMOS Devices," Proceedings of IEEE International Conference on Microelectronic Test Structures , (Monterey, CA), March 2000, pp. 106111.

4. R. Gillon, D. Vanhoenacker and J.P. Colinge, "RF Modeling and Characterization of SOI and Bulk MOSFETs," Proceedings of Workshop on Advances in Analog Circuit Design , (Nice, France), March 1999, pp. V.1V.20.

5. A. Davidson, K. Jones and E. Strid, "LRM and LRRM Calibrations with Automatic Determination of Load Inductance," Automatic RF Techniques Group Conference Digest , (Monterey, CA), November 1990, pp. 5763.

6. T.E. Kolding, "Impact of Test Fixture Forward Coupling on On-wafer Silicon Device Measurements." IEEE Transactions on Microwave and Guided Wave Letters , Vol. 10, No. 2, February 2000, pp. 7374.

7. T.E. Kolding, "A Four-step Method for De-embedding Gigahertz On-wafer CMOS Measurements," IEEE Transactions on Electron Devices , Vol. 47, No. 4, April 2000, pp. 734740.

Troels Emil Kolding received his MSEE from Aalborg University, Denmark, in 1996. Research for his final thesis was conducted with the Wireless Information Network Laboratory (WINLAB) in New Jersey, USA. In 1996, he joined the RF Integrated Systems & Circuits (RISC) Group, Denmark, from where he received his PhD degree in 2000 for his research on on-wafer measuring techniques. Since 1999, Kolding has worked as design engineering manager with the RISC Group and is in charge of the group's large-scale RF CMOS design effort. Areas of specialized research interests include RF CMOS technology, high frequency on-wafer measurements, on-wafer calibration methods, high frequency device modeling and RF CMOS circuit design for wireless applications.

Troels Emil Kolding received his MSEE from Aalborg University, Denmark, in 1996. Research for his final thesis was conducted with the Wireless Information Network Laboratory (WINLAB) in New Jersey, USA. In 1996, he joined the RF Integrated Systems & Circuits (RISC) Group, Denmark, from where he received his PhD degree in 2000 for his research on on-wafer measuring techniques. Since 1999, Kolding has worked as design engineering manager with the RISC Group and is in charge of the group's large-scale RF CMOS design effort. Areas of specialized research interests include RF CMOS technology, high frequency on-wafer measurements, on-wafer calibration methods, high frequency device modeling and RF CMOS circuit design for wireless applications.