Figure 1 Model-based design flow for a wireless receiver.

This article outlines, in four steps, how a small team of engineers reduced design delays and failures through an alternative approach that uses a combination of Model-Based Design and Software Defined Radio (SDR) hardware to design signal processing algorithms, configure RF hardware, generate C and HDL code, and integrate the software with radio hardware. Tools used in this example include MATLAB and Simulink from MathWorks, along with hardware from Analog Devices and Avnet.

Building a wireless receiver is a challenging task that requires a diverse set of skills that are often distributed among many different design teams. In a traditional design methodology, these skills include RF design, HDL programming, system on chip (SoC) development, device driver configuration, and hardware/software integration. With a dependency upon multiple groups, the possibility that the design will fail grows as more team members become involved in the project. Common challenges in wireless receiver design often lead to a design process that has a high potential for miscommunicated specifications and interfaces, incompatible design ideas, and unexplored trade-offs.

Figure 1 shows the steps used to design a receiver using Model-Based Design and SDR hardware. In this approach, a majority of the development effort is spent in the design stage to create a Simulink model of the baseband receiver algorithms. The implementation stage of this process happens quickly because software errors are reduced using code generation, and the SDR hardware provides a configurable RF front-end. Verification time of the code and hardware significantly decreases because the detailed design developed in Simulink accurately reflects the final SDR implementation. An additional benefit of using Model-Based Design is that communication between the engineers is enhanced by working with an executable specification in Simulink, leading to fewer misunderstandings of the overall design and expected performance of the receiver.

EXAMPLE FRAMEWORK

To demonstrate this approach, a team of three engineers used Model-Based Design to develop an Automatic Dependent Surveillance – Broadcast (ADS-B) receiver running on an Analog Devices AD9361 integrated RF Agile Transceiver™/Xilinx Zynq®-7000 All Programmable SoC Software Defined Radio (SDR) platform. This receiver was developed in a relatively short time with minimal obstacles, drawing on the following resources:

- A comprehensive user interface to configure the Analog Devices AD9361 RF Agile Transceiver to receive ADS-B transmissions and obtain a high quality signal.

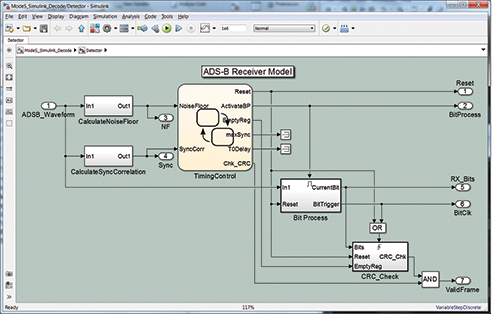

- The ability to build a model of an ADS-B receiver in MATLAB and Simulink that generates functional C and HDL source code (see Figure 2).

- HDL code generation tools that automate many of the hardware/software integration steps.

- Libraries from Analog Devices that enable data communications between the host computer and SDR platform.

Figure 2 Simulink model of an ADS-B receiver.

THE FOUR STEP PROCESS TO PRODUCTION:

Step 1 – Select the Radio Platform

The SDR platform was composed of two key devices. The Analog Devices AD9361 RF Agile Transceiver is a highly flexible, highly programmable device with the tuning range and bandwidth to support a large number of wireless standards, all in a single integrated IC. The Zynq-7000 All Programmable SoC from Xilinx integrates a dual-core ARM Cortex-A9 processor with a large array of programmable logic. Combined, the Zynq and AD9361 produce a versatile radio platform. The transceiver is capable of acquiring many simple and complex radio waveforms, and the Zynq SoC can be programmed to demodulate and decode a wide variety of digital communication protocols.

Figure 3 Captured waveform containing possible ADS-B messages.

Step 2 – Design the Receiver Algorithms in MATLAB and Simulink

MATLAB and Simulink were used to design signal processing algorithms that receive and decode wireless transmissions. ADS-B uses short messages of 112 bits transmitted at 1 Mb/sec and a form of amplitude modulation called pulse position modulation. Detecting and decoding these messages presents several challenges typical in wireless receiver design, including:

- Detecting transmissions of interest using a message preamble

- Aligning the bit detection algorithm to the first message bit

- Making bit decisions based on modulated waveforms

- Calculating a checksum to verify the message is valid

- Decoding the individual bit fields.

The engineers used MATLAB to test a number of design ideas which allowed them to find a promising solution quickly. The design was then converted to Simulink and elaborations were made to the model to increase the clock rate and reduce the area of design.

Step 3 – Verify the Design with Live RF Signals

Hardware-in-the-loop testing provided a good intermediate step to verify that the radio could be configured correctly and the software design remained error-free. Analog Devices provided an IIO System object that enabled the RF signal captured by the Zynq radio platform to be streamed directly into the Simulink model of the ADS-B receiver. This incremental step was useful for verifying that the AD9361 transceiver was configured correctly, proving that the Simulink model could successfully demodulate the live ADS-B transmissions, and confirming that the algorithm design would work over the range of environmental conditions experienced by the radio interface. Figure 3 shows an example of ADS-B waveform data captured off the air.

Step 4 – Generate Code and Verify Real-Time Performance

The C and HDL code needed to program the Zynq SoC was generated from the Simulink model of the ADS-B receiver using HDL Coder and MATLAB Coder. The Xilinx Vivado Design Suite was scripted behind the scenes to download the code to the Zynq radio platform, and then tests were run with pre-recorded IQ data to verify the Zynq code was functioning correctly.

The last step in the design-to-production process was to disconnect from the host PC and verify that the ADS-B receiver would run in real-time on the Zynq radio platform. In this demonstration, the receiver successfully decoded ADS-B transmissions from aircraft at a distance of over 50 miles, as shown in Figure 4.

Figure 4 Live data results from the ADS-B receiver implemented on the Zynq radio platform.

Conclusion

There were a number of elements that contributed to the successful design and deployment of the wireless receiver, including:

- The AD9361 transceiver used in this project is a high performance device that is easy to configure, which eliminated the need to develop a custom RF front-end design.

- MATLAB and Simulink provide a complete signal processing design environment for designing and simulating wireless receiver algorithms.

- The C and HDL code used to program the Zynq SoC were generated from a Simulink model, allowing the engineering team to dedicate most of their development time to the design of the receiver.

- Minimal debugging was rquired because the software code matched the design model, and small, incremental steps could be taken to move the design off the host PC and onto the embedded radio platform.

ADS-B is a relatively simple standard that provides a good test case to demonstrate the Model-Based Design approach to building a wireless receiver. Engineers who adopt Model-Based Design and the Zynq SDR platform should be able to follow this workflow to develop more complex and powerful QPSK-, QAM-, and LTE-based SDR systems.