After exploring various aspects of VRM (Voltage Regulator Module) output impedance ZOUT and related subjects from part 6 to part 11, we now approach the topic from a new angle - how the output impedance of a VRM impacts noise in the time domain. There are many good books, papers and online articles about noise, so I will not talk about noise fundamentals in this post. From the viewpoint of SI (Signal Integrity) and PI (Power Integrity), we will discuss how to manage noise practically.

Noise on VRM Systems

Typically, when it comes to noise, the lower it is, the better off your system will be - if you don’t need to pay any penalty.

In this article, we'll examine those penalties in a low-noise VRM.

We all know the simple rules below on how to handle noise:

- Lowering the (VRM output) impedance of an output node lowers the noise of the node

- Increasing the bias current flow of a node lowers the noise

- Running at cooler circuit/PCB temperatures lowers the noise

Rule 1 above refers to a method of reducing noise. A simple and effective way to reduce noise is to add noise bypass capacitors to your target node.

Rule 3 directly refers to thermal noise.

Finally, rule 2 is a trade-off between rules 1 and 3. By increasing the bias current flow of the circuits, we are reducing the impedance of the target node by following Ohm’s law: V = R × I

When an operating bias "voltage" point stays the same, increasing the current "I" means lowering the impedance "R". Interestingly, increasing bias current flow pushes up the system's power consumption or power loss, resulting in an increase in the board's temperature and higher thermal noise.

Getting back to the rule 1, our simplest action is adding capacitors, but we have reviewed in this series that a VRM offers a low output impedance.

Increasing VRM Loop Capacitance

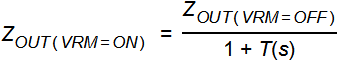

Typically, in VRM systems, the ZOUT(VRM=OFF) term corresponds to the output capacitors. According to Eq.9-1, the output capacitor impedance can be reduced by the VRM loop gain within the regulator's bandwidth. This is a significant impedance reduction.

Equation 9-1 from the Part 9

VRM acts as an active noise canceling block at its output node, which is why we find many LDO (Low Drop Out) regulators near the noise-sensitive RF and signal chain devices.

This benefit of ZOUT(VRM=ON) is very important compared to a simple placement of capacitors. The basic mechanics of how additional capacitors contribute to noise reduction is by forming an RC filter. This filter isolates an upstream power / bias source circuit by a certain amount of resistance R, which can be an explicit resistor element or an inherited source’s output impedance. The target node impedance is then reduced to a very low value by a capacitor C, further reducing noise.

Fig 12-1 An RC Filter as Noise Bypass

When dealing with PI or power distribution network (PDN) impedance, our impedance of concern is well under one ohm (1 Ω), and we can easily find that an RC filter is ineffective.

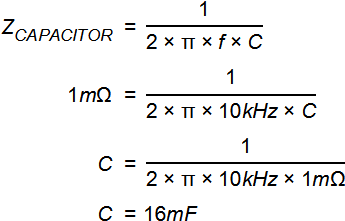

As we reviewed in this series, we can only manage our PI events within our VRM’s control loop band-width (BW), typically in the 100kHz range. As a simple example, let’s aim for 10 mΩ at 10kHz by adding a single capacitor.

Eq.12-1

This is not an error. We indeed need 16 millifarads to meet this easy-looking target of 10 mΩ at 10kHz. With the power of a VRM’s loop gain, as shown in Eq.9-1, we can use a realistic capacitor and hit the target when we use a VRM properly.

This simple equation Eq.12-1 illustrates one important fact dealing with PI:

Bypassing noise gets harder as our frequency of concern decreases.

When we talk about "noise", many engineers think about the megahertz (MHz) to gigahertz (GHz) range of noise in the course of EMI (Electro-Magnetic Interference) or EMC (Electro-Magnetic Compatibility) discussions or standards. The noise range of MHz to GHz is indeed challenging to handle, but handling noise at kilohertz (kHz) or lower frequencies is also difficult due to this unrealistically huge capacitor demand. For reference, this is exactly the same frequency range that many audio enthusiasts are continuously working addressing. Many noise-reduction techniques in the audio world are applicable to our PI noise, especially with our measurement setup.

Eq.12-1 refers to output power rail noise, but this challenge applies to power printed circuit boards (PCBs) everywhere. For example, we need to use a relatively huge amount of noise bypass capacitors at our voltage reference (VREF, or simply bandgap reference) sub-block in our VRM systems. To achieve a low noise VREF for our modern PI projects, the same equation suggests at least 10 nF (or 10,000 pF) noise-bypassing capacitance, which is too big to integrate inside IC devices. That's why many higher-end LDO devices recommend using an external noise-reduction capacitor in the 10nF range.

Power Integrity = Balancing Trade-Off Factors

Many years ago, before this PI movement happened, I wrote an application note about LDO noise, examining it in detail.[1]

In this paper, I provided insights into minimizing the output noise of an N-type MOS-FET output stage LDO device. The recipe was simple: increase noise bypassing capacitors in the right places of its VREF and noise-gain stage. Now, with all the knowledge of PI, I would like to revise my past work.

One of the most important lessons from PI is to avoid any peaking on the VRM’s frequency domain characteristics.

Here, we want;

a flat output impedance / PDN impedance,

a flat output noise density,

and a flat PSRR.

Every VRM system is designed to power up other load devices. Our final application system, which combines multiple VRMs and loads, thus exhibits combined frequency-domain performance characteristics related to these factors. Whenever we have frequency-domain peaking on a stand-alone VRM characterization result, such a peak possibly interacts with its load devices to peak out, which is recognized as a PI challenge.

Looking back at my article [1] - "Oh, no!", I did cause a big noise peak. When I wrote it, I aimed to minimize the DUT’s RMS (Root-Mean-Square) noise of 10 Hz to 100 kHz integration. And I did have sharp noise peaking at 500 kHz.

Which brings up another important lesson from our PI practice:

Everything you do to optimize one PI factor is a trade-off of one or more other PI factors.

When you max out one parameter, you will need to pay the cost in another area. In my case, I chose the lowest 10 Hz - 100 kHz RMS noise for a penalty of noise peaking at 500 kHz.

Strong Linkage between ZOUT and Output Noise

In this article, we have two (2) bench experiments illustrating how a VRM output impedance ZOUT forms its output noise.

In a typical VRM device, we have two or three stages of a control loop system where the simplest one is a linear regulator or LDO regulator consisting of one VREF, one error amplifier (EA) stage and one output transistor stage. In contrast. an SMPS (switch mode power supply = switching regulators) has multiple VREFs, voltage-loops, current-loops, and/or output transistor stages.

With the connection of electrical nodes between these stages, we start with a finite amount of thermal noise as an output from the upstream stage, and this white noise interacts with the node impedance. For simplicity (as this is not an academic paper), we will only focus on thermal noise here. If there is absolutely no movement of electrons (charge), we’ll observe zero noise. Conversely, as we observe visible amounts of noise, we must have a certain amount of electron movement.

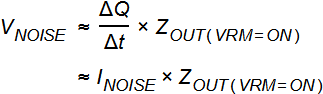

Eq.12-2

Eq.12-2

Eq.12-2, we assume the INOISE has a white noise characteristic, where it shows very flat power over a broad, wide frequency range.

Don’t we remember this bold font statement? Does it sound very familiar to us?

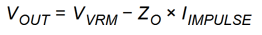

In part 10, we reviewed an impulse load transient response, where the impulse has flat power over the broad frequency spectrum. The only difference between white noise and the impulse is that white noise has a totally random phase over the frequency range where an impulse has very uniform phase.

Besides a DC bias term of VVRM, both Eq.12-2 and Eq.10-2 suggest we can see the shape of ZOUT(VRM=ON) from the noise plot.

Equation 10-2 from part 10

Output Noise Bench Test #1: N-Type MOS-FET Output-Stage LDO

When applicable, a linear regulator with an N-type MOS-FET output transistor is a good choice compared to P-type regulators, as an N-type device is less sensitive to a capacitive load.

Yet, when we put too much capacitance, an N-type LDO starts showing its own sensitivity to capacitive elements.

A fundamental mechanism of this N-type regulator robustness comes from its output stage being a voltage-follower / source-follower / emitter-follower. A voltage-follower circuit has a solid reputation as a robust power-sourcing block. There is a lot of information online teaching us how a voltage-follower starts showing gain peaking together with excessive capacitive load. Still, this short technical blog [2] explains everything we need to know very simply.

By placing capacitors everywhere to increase noise bypassing, we end up making a good Colpitts oscillator.

Even though it was not oscillating, my previous project was precisely on this course.

For the first bench test, we use an N-type MOS-FET LDO evaluation board as our DUT. And we run the tests detailed in the following 2 × 2 matrix for a total of four measurements.

| × |

|

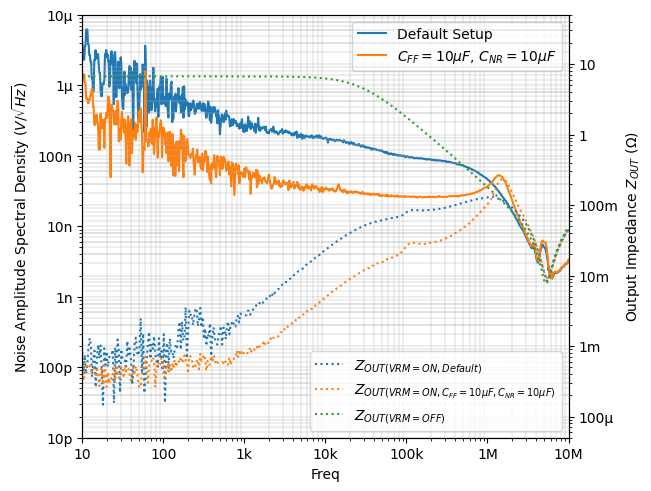

We have the result in Fig 12-2, where the first (left) axis shows the output noise with solid lines, and the second (right) axis shows the output impedance with dotted lines. These two axes are intentionally adjusted to overlay the peaks.

10-100kHz | 100-100kHz | 10-10MHz | 100-10MHz | |

Default Setup | 45.33 µVRMS | 43.00 µVRMS | 87.87 µVRMS | 86.70 µVRMS |

CFF=10μF, CNR=10μF | 10.19 µVRMS | 9.56 µVRMS | 54.85 µVRMS | 54.73 µVRMS |

In Fig 12-2, we can clearly see that the setting of CFF=10μF and CNR=10μF generates peaks in both plots of output noise spectral density and output impedance even though we see no peak with the "Default Setup." Furthermore, we can observe that the shape of the peaks is very similar to that suggested by Eq.12-2 and Eq.10-2.

In the RMS table, we can judge this CFF=10μF and CNR=10μF setting as the overall winner, but we need to pay attention to whether the peak goes any higher/sharper. With an increased peak, the RMS noise number of 10Hz to 10MHz integration or 100Hz to 10MHz integration may exceed its "Default Setup."

Or, if your frequency of noise concern is around 1MHz region, Fig 12-2 tells you that you want to use the "Default Setup" to avoid peaks.

When you carefully review the datasheets of many "low noise" VRMs on the market, you will find this kind of high-frequency peak.

Output Noise Bench Test #2: P-Type MOS-FET Output-Stage LDO

We use another linear regulator with a P-type output transistor in our second bench test.

In applications where PCB area is limited, many engineers wish to cut down the number of VRM input and output capacitors compared to the recommended targets from their vendor. Recently, while brainstorming a new project idea, I took a deep dive into this subject and collected this data.

The DUT is a 5 V input voltage, 500 mA output P-type FET LDO. The vendor recommends using 1 μF of output capacitance but we want to use a smaller size capacitor to save PCB area if possible.

So, I tested three different capacitor values (1 μF (Default), 0.33 μF, and 0.1 μF) for output spectral density and output impedance, just like bench test #1.

All the P-type LDOs form their first pole from the pairing of the output capacitor COUT and the combined impedance of the output node (consisting of a load impedance, P-type FET’s ON impedance and everything connected to the output node). When we reduce the output capacitance COUT, this pole moves toward higher frequency, which automatically extends its control loop bandwidth but makes its phase margin worse.

We have the result in Fig 12-3, where the first (left) axis shows the output noise with solid lines, and the second (right) axis shows the output impedance with dotted lines. Again, these two axes are intentionally adjusted to overlay the peaks.

Fig 12-3 Bench-Test #2: P-FET LDO Linkage between ZOUT and Output-Noise

Fig 12-3 Bench-Test #2: P-FET LDO Linkage between ZOUT and Output-Noise

These are the key observations:

- As in bench test #1, the curve shapes of noise density and output impedance are very similar and the peak position matches.

- During the test, we confirmed that all three conditions have NO self-oscillation.

However, with 0.1 μF capacitance we see a forced oscillation by injecting a perturbation signal for the output impedance measurement.

Because of this forced oscillation, the blue dotted line output impedance curve shows ugly peaks. By judging from the corresponding noise peak, its true ZOUT peak comes in between 6MHz and 7MHz. - Citing the prior explanation for how the first pole moves, we can observe ZOUT peaks move toward higher frequency and become sharper. This indicates that the loop bandwidth extends and the phase margin reduces.

⇒ Please refer to part 9 where we reviewed that ZOUT is a direct measurement and indicator of a control loop transfer function. - Besides its forced oscillation at 6MHz, the 0.1 μF capacitance setting shows a higher value compared with the other 2 curves, and flat ZOUT of ~50 mΩ in the lower-frequency region. This indicates that its VRM control loop does nothing, and it is another indicator that this setting is not usable.

- It is wise to follow the VRM vendor’s recommended usage.

[2] Emitter followers as Colpitts oscillators, (John Dunn, EDN.com, July 24, 2012)