Many engineers in the RF and signal chain fields think of a Voltage Regulator Module (VRM) system as a "power supply", a totally different animal from their signal chain electronics components. Let’s find some common ground between RF/signal chain engineers and power engineers.

When we see the structure of VRMs, from simple linear regulators or LDO (Low Drop Out) regulators (or simply LDOs) to a complex SMPS (Switched Mode Power Supply = switching regulators), one can find an error amp (EA) in a negative feedback loop as its key regulation element (Figure 1). Keeping our focus on this EA, we can trace its positive input port back to a voltage reference "VREF" and we see its negative input port connected to the output voltage via a scaling resistor network as necessary. Small changes to the feedback signal cause corrections to the output through the power stage, so from this EA-centric viewpoint, VRMs are just power amplifiers of special kind.

This viewpoint gives us a better understanding of VRMs from the analogy to amplifiers dealing with "signals". All the same concerns an RF or signal chain engineer has are applicable to VRMs, as a special kind of power amplifier. This statement "a VRM is just a PA" brings us to one immediate simple outcome: If your "VREF" moves to a different DC level or if it has AC superimposed, it’s seen as a "signal" to amplify.

A VRM is just amplifying its "VREF" voltage by its designed gain. For example, many step-down (buck) regulators of 5V or 12V input produce an output of 3.3V using a 0.8V reference voltage and therefore have a gain of "× 4.125" (= 3.3V / 0.8V). As our VRM is a "× 4.125" gain amplifier, what happens if our 0.8V "VREF" has 0.5% error? 0.5% error of 0.8V "VREF" means we have a 4mV error to be amplified by "× 4.125" resulting in a 16.5mV error in the 3.3V output which is, of course, 0.5% error from the target output voltage.

When "VREF" moves in the frequency domain the effects are interesting to review.

When "VREF" moves in the frequency domain the effects are interesting to review.

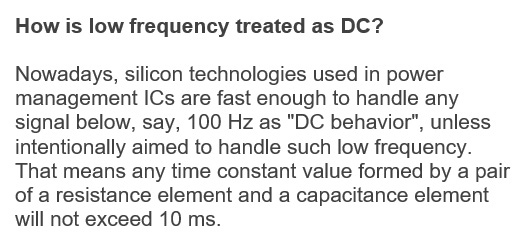

In this series of articles, we treat a response of any example circuit at 1 Hz or 10 Hz as DC behavior without further notice.

If our VRM’s "VREF" has white noise superimposed to a high frequency, say, up to 10 MHz, it tries to amply this white noise as its input signal (again, the "VREF" goes to the positive "+" input of the EA as a "signal"). Note that we are talking about a hypothetical use of a VRM which would not be desirable in practice.

Will we have a white noise "output" from the VRM up to 10MHz? The answer is "NO".

Here, we need to factor in the negative feedback control loop bandwidth (BW) of this VRM system. As we form a negative feedback loop in our VRM, we only have a limited flat gain BW and, beyond that frequency point, our gain goes down by just following its Gain-Bandwidth product characteristics. Our VRM, as a PA, can amplify the "VREF white noise" according to this gain profile. This statement is applicable to this entire series of articles: "Your VRM does increasingly little for you outside its feedback control bandwidth."

Gain-Bandwidth Product of a VRM

This example simulation illustrates the gain bandwidth of a VRM as a PA (Figure 3) derived from the simulation schematic shown in Figure 4.

This simulation deck can be downloaded from the Qorvo repository at GitHub.

Figure 3: A typical LDO gain-bandwidth plot

This P-FET LDO model compares its "open loop gain" and "closed loop gain". This LDO is designed to have a 5V output with an internal 0.5V reference voltage (VREF), so it is a “×10” amplifier from the view point of the voltage VREF. By thinking of it as a "×10" amplifier of VREF, the AC simulation source "Vac" is placed in series with VREF. Though we labeled it "Vac", we can also see it as a noise source added to VREF, following the previous section of this article.

The LC pair ("Lopen", "Copen") is working to open/close the loop. When "closed" at x=0, the feedback signal from Rfb // Rg goes to the error amp "A1" as it is. When "open" at x=1, the feedback signal from Rfb // Rg goes through this strong low-pass filter and only the DC bias point is set by the error amp "A1".

In the frequency domain, once any signal or noise, or any dynamic signal, goes beyond the full gain BW, and the phase response drops away, the VRM responds less and less …and ultimately can do nothing as a PA.

Many engineers expect something better from their VRMs beyond the loop BW. For example, many IC vendors list a PSRR performance of their LDO devices to a very high frequency. A very good LDO device has its loop BW up to 1 MHz range, or slightly higher, but beyond that frequency point, the LDO has no response. What we can see on its PSRR plot, beyond the BW, is a performance of its output capacitor. We would have the same PSRR curve beyond this unity gain frequency point even if we turn OFF the LDO.

The flip side of this discussion is that your VRM does amplify this "white noise VREF" up to its bandwidth, observed as "VRM self-generated" noise. This story sounds the same or similar to a discussion about "low noise amplifiers" (LNAs) in RF or signal chain applications, but is not the same. As we reviewed earlier, this noisy “VREF" is a valid input to the voltage regulation amplifier output and the VRM is forced to amplify the VREF voltage by its gain. In contrast, a LNA noise is defined as unforced noise added to its output by shorting its positive and negative inputs. This difference gets highly magnified when your VRM outputs a high output voltage rail. A 24 V output VRM based on its 1.2 V reference block is a × 20 gain amplifier, or × 20 gain "VREF noise amplifier". In this context, we can derive a simple rule of thumb: If possible, use as high a reference voltage as possible to avoid "VREF noise amplifying action".

For an example of lowering the gain of a VRM as a power amplifier, Qorvo’s ACT40850 is designed to use a 4V reference, very well noise filtered, to generate its output of 20 to 55 V (Figure 5).

Check out https://p.qorvo.com/qspice.html to sign up for an early copy of QSPICE - a newly written and upgraded SPICE based simulation package.