Modern wireless communication systems demand not only high efficient RF and microwave amplifiers, but wideband designs too. Switchmode power amplification classes can provide both benefits simultaneously, but theoretical knowledge must be combined with important practical considerations to get these advantages.

There are important practical considerations that limit the theoretical capabilities of amplification classes explained in the literature, especially in wideband conditions. Even though some technical solutions have been proposed to overcome these practical limits in narrowband designs, the exigent demands of wideband operation turn them useless. In this paper, the most relevant practical considerations that must be taken into account for proper high efficiency switchmode wideband solid-state power amplifier (SSPA) design are analyzed and solutions are proposed for the proper class of amplification implementation.

SSPAs and low load impedance

In order to simplify radio transmitters and to reduce the size and complexity of power combiners and splitters, the solid-state industry has designed and released microwave transistors as powerful as possible within the limits of current solid-state technology. At the present, Si and GaAs, and more recently GaN and SiC technologies, dominate the solid-state RF and microwave power transistors market. Regardless, the solid-state technology, maximum power per transistor will always be limited by thermal and electrical limits such as breakdown voltage and balanced heat dissipation.

The thermal limits of power RF and microwave transistors are derived from the thermal resistance and heat sinking capabilities of semiconductor materials and packages. These limits can be overcome to some extent by electronic technology using highly efficient switchmode amplification classes because their inherent high power efficiency contributes to reduce heat generated in transistors.

Modern, commercial grade, RF and microwave transistors exhibit breakdown voltages ranging from 50 to 150 V for Si and GaN technologies and lower breakdown voltages for GaAs. These breakdown voltages impose a limit to the power supply voltages of practical SSPAs to about 24 or 50 V, depending on the peak to average voltage ratio of the amplification class chosen to design the SSPA.

Breakdown voltage determines the load impedance required by one power transistor to deliver a specific output power level, POUT, in such a way that the lower the breakdown voltage of the transistor the lower the load impedance required to get a specific output power level POUT. Using current solid-state technologies, load impedances are typically below 50 ohms at power levels as low as 10 W and below 5 ohms for power levels about 100 W.

Low load impedances and their inherent high current levels are not only related to high power losses, the effect of parasitics (mounting and packaging) are strongly evidenced by high current levels. The correct implementation of any amplification class is difficult in low load impedance conditions, but more specifically the implementation of amplification classes demanding complicated load impedance profiles versus frequency (for instance, Class F). This difficulty increases as frequency and bandwidth increases, making the perfect implementation of any “text-book” amplification class very complicated in practice with maybe the only exception of Class A.

The most relevant parasitics and practical considerations that make difficult the correct implementation of wideband switchmode amplifiers at RF and microwaves are the following:

a) Parasitics of transistors’ packages: RF and microwave power transistor packaging is a convenient way to integrate power solid-state transistors in low cost Printed Circuit Boards (PCB) based on plastic laminates. Nevertheless, the packages of power transistors add important parasitics to the dies that heavily affect their electric behaviour not only at microwaves but at frequency bands as low as VHF or high HF. Accurate modelling of power transistors’ package parasitics is not simple, nevertheless, for the sake of simplicity. Figure 1 shows an approximate yet effective electrical package model directly extrapolated from the transistor package physical structure.

Figure 1 Simplified high power RF package model and typical parasitics values.

The series inductive parasitic is usually the most disturbing one for the implementation of any class of amplification. The electrical connection from the die to the boundaries of the transistor package is usually made of a set of paralleled gold bond wires and a metallic tab. From a simplified electrical point of view it can be modelled as a 0.4 to 1.5 nH series inductance and a 1 to 3 pF shunt capacitance to ground.1 Therefore, the reactance of the series inductance of an RF average transistor is about +1j at only 200 MHz. This value is a noticeable fraction of the load impedance required by a power transistor operating on low load impedance conditions. Moreover, this parasitic cannot be easily absorbed by the load network of the amplifier.

One of the most important adverse effects caused by this parasitic is that it is impossible to connect any shunt load (capacitance or inductance) directly to the drain of the transistor. This severe restriction makes the correct implementation of most amplification classes difficult with the only exception, Class A. This restriction is even more noticeable in wideband amplifiers that usually require bandpass derived load networks using shunt components.2

Although this article is not focused on driving circuits, it is clear from above that a similar analysis can be performed for the parasitics at the input of power transistors. From the reasons exposed before, it easy to derive that the possibilities of synthesizing specific driving waveforms suitable for efficient switchmode amplifier driving at RF and microwaves are severely limited.

Figure 1 shows a simple yet effective electric model for a typical packaged power transistor. Typical parasitic values for approximately 100 W packaged devices intended for under 1 GHz operation are also displayed.

b) Transistor intrinsic output capacitances: Transistor output capacitance causes two important effects:

- It limits the maximum frequency or bandwidth (for a determinate POUT) for nominal implementation of amplification classes requiring capacitive or short-circuit load at harmonics, such as Class E, Class C and mixed modes.

- It makes difficult, degrades or precludes in extreme cases, the implementation of amplification classes requiring frequency alternated load impedance versus frequency profiles: Short circuits at even harmonics and open circuit at odd ones (or vice versa). Some clever load circuits have been devised to overcome these effects at least at 2f0 and 3f0;4 unfortunately, to the best of the knowledge of these authors, those techniques are only effective for narrow bandwidths.

Figure 2 Comparison of a Si LDMOS transistor |X(Coss@24V|, |X(Lpd)| and RL.

Figure 2 shows a comparison of the module of the reactance of COSS at 24 V |X(COSS at 24 V)| of a typical Si LDMOS commercial transistor and the module of the reactance of its inductive drain package parasitic |X(Lpd)| versus the resistive part of the recommended load impedance RL for this transistor. As can be observed, both parasitic reactances are noticeable fractions of RL at only 200 MHz.

c) Effects of lumped component parasitics on the synthesis of SSPA’s load networks: Two important figures of merit of passive lumped components (inductors and capacitors) used in SSPA load networks must be considered in SSPA design: Self Resonant Frequency (SRF) and Quality Factor (Q).

Capacitors: Multilayer ceramic or porcelain dielectric capacitors are frequently used in the load networks of SSPAs. For a specific capacitor package, the SRF decreases as capacitance increases; the higher the capacitance the lower the SRF. Regarding Quality Factor Q, this figure of merit usually decreases as frequency and capacitance increases. This peculiar performance causes two important effects:

- The Q versus capacitance profile causes important power losses in the low load impedance environments typical of RF and microwave power transistors for SSPAs.

- The Q versus frequency profile (Q decreases as frequency increases) causes that the power losses of the SSPA load networks at the harmonics are higher than at the fundamental.

- The high value capacitors required by SSPAs at low impedance planes exhibit low SRF values that make the correct synthesis of the load impedance difficult at the harmonics.

Inductances: Q and SRF of inductances are not easily predictable. In addition to ohmic losses, radiation losses have an important role in these figures of merit. Even though it is usually true that the Q of a specific inductor increases as frequency increases (while the SRF is not reached), there is not a direct rule linking Q and inductance.

To illustrate these effects, Table 1 shows the SRF and Q of some SMD multilayer porcelain power capacitors for different capacitances and frequencies and some air core inductances required by the load network of a typical SSPA in the 100 W range. It can be observed that the large capacitors exhibit not only relatively low Q—not much different than the Q of the inductances—but low SRF as well.

In summary, the effects of component parasitics on SSPAs look “amplified” by the high current levels involved in the typical low load impedance planes required by SSPAs. It can be said that, in some way, the technological problems associated to low load impedance planes typical of SSPAs look like the problems that appear using low power devices at higher frequencies. Therefore, the technology required to work in high output power conditions is not different than the one required at much higher frequencies using low power devices that demand higher load impedances (non-packaged transistors, single layer capacitors, etc.). As a matter of fact, MMIC or hybrid technology is probably the most suitable technology for high power SSPAs at frequency bands as low as VHF to properly implement any amplification class. Nevertheless, SMD technology over plastic PCB laminates is the dominant one because it is inexpensive.

When the power levels delivered by transistors are high and frequency is also high, as happens in RADAR or broadcast applications, the effects of package parasitics are so important that they preclude the correct implementation of any amplification class except for very narrow bandwidths. Built-in matching networks are frequently used to solve this problem, but this solution limits the freedom and possibilities for the designer.

Built-in matching networks (internally matched transistors):

In order to keep the practical advantages of SMD manufacturing technology on plastic laminates with high power amplifiers at frequencies beyond UHF, solid-state manufacturers include built-in matching networks into many of their high power transistor packages, both at their input and output. These built-in networks are impedance transforming networks made of micro lumped elements (MOS capacitor for capacitances and bond wires for inductances) connected next to the transistor die. The main purpose of these built-in matching networks is elevating the input impedance and output load impedance required by transistors, making it easier for the implementation of output load impedance networks and increasing the wideband operation capabilities of the devices.

Nevertheless, transistor built-in matching networks cause some problems and have limits. The possibilities of synthesizing a determinate load impedance profile at the fundamental and harmonics are severely limited by built-in matching networks because the high frequency impedance “trend” of the built-in matching network, located next to the die, imposes the high frequency harmonic “trend” of the load network.5 Therefore, the possibilities of implementing different amplification classes using transistors fitted with built-in matching networks are limited. As a matter of fact, these “pre-matched” transistors behave like amplifiers rather than simple transistors. Furthermore, built-in matching networks add extra power losses to transistors, contributing to reduce the efficiency of the SSPA using these kinds of devices.

Load Circuits

Load circuits are used in SSPAs to provide the proper complex load impedance at the fundamental (usually performing impedance transformation functions), besides providing proper termination at the harmonics.

Impedance transformation tasks are usually carried out by two different types of circuits:

Passive impedance transformation networks based on lumped components and transmission lines6 or transformers (based on magnetic coupling or transmission line technology).7 Both types of circuits and devices will be briefly analyzed in the next few subsections.

Impedance transformation networks based on lumped components and transmission lines:

SSPA load networks made of lumped components and transmission lines usually combine the impedance transformation and harmonic termination tasks. When these functions have to be implemented over wide bandwidths (one octave or more), load networks become quite complex, usually requiring more than six elements to achieve an acceptable flat “in-band” response and consequently those load networks cause noticeable power losses.

Low reactance components are required in the load networks of high power transistors. As previously mentioned, these components suffer from low SRF and Q problems, contributing to make difficult the correct load synthesis at the harmonics and causing power losses. These components also cause circuit repeatability problems because even small value changes and component placing tolerances cause noticeable changes in the synthesized load impedance both at the fundamental and harmonics.

Because of all the reasons mentioned, combining the wideband load impedance transformation and harmonic termination tasks into one load network made of lumped or transmission line elements is not always the best technical solution for high efficiency SSPA loading, especially if the load impedance transformation ratio is high. Not only it is difficult to synthesize the proper load impedance profile required by the SSPA at harmonics, but power losses in the load network can mask the theoretical power efficiency benefits provided by high efficiency amplification classes.

Transformers:

Unlike other impedance transforming devices and circuits, transformers exhibit important practical advantages for SSPA load networks such as wideband operation (ideally infinite), compact size and low power losses, usually lower than the losses caused by equivalent impedance transformation networks based on lumped or transmission line elements. Transformers have been used for decades as impedance transformation devices in SSPAs. Two different transformer technologies are used at RF and microwaves bands: Conventional transformers (magnetic coupling)8 and transmission line transformers.7

With some exceptions (Class A and push-pull Class B) transformers cannot be used alone to implement SSPA load networks; additional harmonic termination networks are required for amplification classes such as Class C, D, E, etc. Separating impedance transformation from the harmonic termination functions in SSPA load networks using a wideband transformer for impedance transformation and a lumped component or transmission line network to provide harmonic termination has proven to be useful and efficient in SSPA load network design techniques8 that can be used with both conventional and high efficiency amplification classes. This technique relieves the lumped component or transmission line termination network of impedance transformation tasks and allows using it just to provide the proper load phase angle at the fundamental and termination at the harmonics.

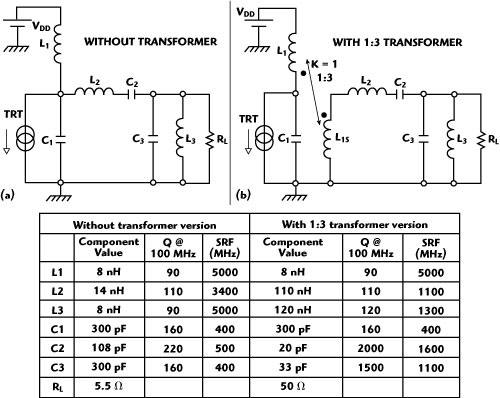

Usually only six element networks are sufficient to perform the harmonic termination functions required by any amplification class over bandwidths about one octave, yielding second harmonic rejection better than -20 dBc and bandpass ripple better than 0.1 dB. Because of the low number of components required by these mixed load networks, their power losses are low and can be further minimized if the transformer of the load network is located next to the power transistor and the harmonic termination is cascaded after the transformer (at a higher load impedance plane), as shown in Figure 3. This way the reactance of the components required by the termination load network is high. Small capacitors and large inductors can be used that exhibit better SRF and Q figures than the low reactance components required at the low impedance plane next to the power transistor reducing currents across components, lowering power losses and decreasing the impact of parasitic effects on load impedance synthesis. Figure 3 shows two implementations of an equivalent wideband Class B single end SSPA: A lumped component load network implementation and a mixed load network made of a transformer and a harmonic termination network. The quality factor Q and SRF of their respective components are also shown in Figure 3.

Figure 3 Wideband class B amplifier implementations with lumped components only (a) and mixed transformer and lumped components (b).

Conventional transformers have been successfully used for years as impedance transformation devices for SSPA load networks from HF to VHF.8 “Macroscopic” conventional coupled transformers suffer from parasitics such as leakage inductance. These parasitics limit the maximum operating frequency and bandwidth of the transformer especially in low load impedance planes. Therefore, even thought it is not completely impossible, conventional transformers are rarely used in load networks for SSPAs at UHF and higher frequencies.

Transmission line transformers take advantage of the magnetic and electric coupling properties of transmission lines7 to improve the performance of conventional transformers at high frequencies. They can be used from HF to mid UHF, but are rarely seen in the microwave region, at least based on typical building techniques (using pieces of coaxial cables connected in series or parallel). Nevertheless, conventional (magnetic coupling) and transmission line transformers can also be built in the microwave region using hybrid or MMIC technology.9

Besides impedance transformation, other important uses of transformers in SSPAs are the implementation of push-pull amplifier circuits. Push-pull technology can add important practical benefits to SSPA design when it can be used. As a matter of fact, the majority of the most powerful SSPAs in the market are based on push-pull technology.

Push-pull RF and microwave SSPAs

In the push-pull topology, two transistors are driven with 180 degrees phase difference and share the same load. Usually transformers are used with push-pull topologies to convert unbalanced loads into the balanced loads required by push-pull amplifiers besides providing impedance transformation functions.

Many high power SSPA stages are based on push-pull technology. When very high power levels are involved, push-pull technology is usually the choice for SSPA design. Several technical advantages are attributed to push-pull topology, including direct combination of power delivered by two power transistors operating in phase opposition into one load occupying a small footprint, attenuation of the even harmonics of the amplified signal, load impedance doubling (compared to a single ended amplifier delivering the same power level at the same voltage), etc.

Nevertheless, push-pull topology is not compatible, from a theoretical point of view, with all amplification classes, at least in its direct implementation. Moreover, even amplification classes compatible with push-pull technology exhibit important practical implementation difficulties because some of the parasitics covered previously.

Figure 4 Voltage switching class D amplifier schematic, waveforms and load profile.

Class B and D (both voltage and current switching) are examples of amplification classes directly compatible with push-pull technology. Push-pull circuits provide an alternated load impedance versus frequency profile (from a non-alternated frequency load impedance) required by Class D. Figure 4 shows this effect on a voltage switching Class D amplifier using ideal switching transistors and a transformer. Voltage and current waveforms and load impedance versus frequency profiles are shown at the primary and secondary of the transformer to point out the harmonic load alternation behaviour associated to the push-pull operation.

Harmonic load impedance alternation versus frequency is essential for some amplification classes such as Class D, but it is not admitted by other amplification classes requiring homogeneous (non-alternated) load impedance profiles at harmonics such as Class E.3 There are several examples of push-pull Class E amplifiers in the scientific literature, but by analyzing them it is easy to derive that the load is not directly connected across the drains of the two transistors of the amplifier, as happens in push-pull Class B or D amplifiers, but across branches of the circuit where current is sinusoidal. Therefore, in these push-pull designs, two currents of the same amplitude and 180° phase difference are combined, not the non-sinusoidal drain currents inherent to Class E amplification. Obviously, the load profile at the harmonics is not important if only sinusoidal currents are combined.

This is an important difference. In some ways it can be said that these so-called push-amplifiers that combine sinusoidal currents obtained from the branches of two amplifiers driven in 180º phase difference, instead of combining the non-sinusoidal current of the transistors drains, are not pure push-pull designs, but sets of two transistors combined in phase opposition using transformers as combiners. This power combining concept resembles in some way the hybrid combiner10 without the isolating resistor.

Figure 5 Typical push-pull class E amplifier, waveforms and load profile.

Figure 5 shows a typical Class E push-pull amplifier using ideal switching transistors and a transformer. Load profiles versus frequency at different impedance planes and voltage and current waveforms are shown too.

There are practical considerations that make difficult the implementation of push-pull topology even using the amplification classes that accept the direct connection of loads across the drains of the transistor pairs such as Class D. Push-pull amplification is also affected by the parasitics of transistors and transformers described previously. For instance, transistor output capacitance has an important impact on the performance of Class D. This reactance is located from the drain to source of each transistor of the push-pull pair, not from drain to drain. The load profile provided by this parasitic capacitance to the transistors of the push-pull pair from drain to ground is homogeneous (not frequency alternated) degrading the open circuits of the alternated load frequency profile provided by the push-pull circuit. This is one of the reasons the practical implementation of Class D amplifiers at RF and microwave frequencies is difficult. In practice, this capacitance causes many of the so-called Class D amplifiers at high frequencies to not operate in a pure mode, but a mixed mode between Class E and D.

Low pass harmonic filters

The harmonic attenuation provided by wideband switchmode SSPA load networks, usually designed as bandpass circuits, is not sufficient to fulfil the requirements of modern communication services, demanding harmonic attenuation levels better or equal than 50 dBc.

The more complex the load network of the switchmode power amplifier, the better its harmonic rejection capabilities at the expense of higher power losses. Usually a tradeoff is required for designing the load network of SSPAs in order to balance its harmonic attenuation capabilities and power losses. From a power efficiency point of view, using a low pass harmonic suppression filter after the amplifier load network provides better results than designing a more complex amplifier load network. Nevertheless, care must be taken in this power budget because if the harmonic attenuation provided by the load network itself is not high (20 dB or lower), a low pass filter located at the output of the transistor (among the amplifier and the load) to clean up the output spectrum may change the amplifier performance and even the class of amplification implementation.

Reflective and absorptive filtering technologies can be used to improve the harmonic attenuation performance of power amplifiers. Reflective technology filters “reflect” the energy at the harmonics back to the amplifier. This technology is the most widely used in practical circuits. In theory, the reflected energy at the harmonics by the low pass filter should be converted into energy at the fundamental in the amplifier, but in practice this energy can degrade the amplification class implementation and consequently the amplifier performance. This is because a reflective filter exhibits pure resistive impedance over its pass-band but reactive impedance over its attenuated band, changing the resistive load conditions required by the load network of the amplifier at the harmonics. In practice this effect is only noticed if the harmonic attenuation provided by the load network of the amplifier is not too high (20 dBc or less).

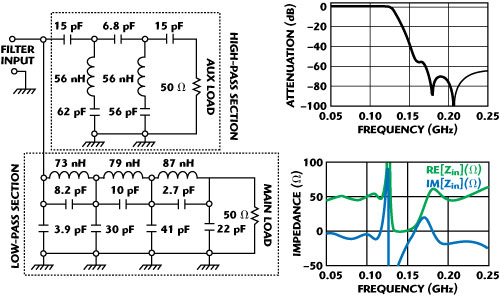

Figure 6 Diplexer harmonic rejection filter stage for a FM broadcast power amplifier and input impedance vs. frequency.

On the other hand, more elaborated absorptive filters, usually based on diplexer technology, provide resistive load impedance to the load network of the amplifier both at the fundamental and harmonics, and consequently do not change the performance achieved by the amplifier without low pass filtering stages. Figure 6 shows a diplexer harmonic filter stage for a FM broadcast power amplifier. It also shows its frequency response and the impedance versus frequency profile provided by this circuit both at the fundamental and harmonics.

Conclusion

Many practical considerations, most of them related to the parasitics of transistors and passive components, make the implementation of amplification classes difficult, especially when high power transistors are involved. RF and microwave power transistors usually require very low loads because of the relative low breakdown voltages of currently available solid-state power technologies. Low load impedance conditions amplify the effect of the parasitics and make the implementation of many amplification classes difficult, or degrade or even preclude them, especially in wideband conditions at frequency bands as low as VHF or even high HF.

Mixed load networks for SSPAs made of transformers plus harmonic termination networks are usually more efficient than complicated load impedance transforming networks made of many lumped components or transmission lines. The push-pull topology is an option to consider in order to achieve more powerful amplifiers, but the limits imposed (not by practical considerations but theoretical limits too) must be known because push-pull technology is not compatible with any amplification class.

Low pass filters used to improve harmonic attenuation at the output of the amplifier (especially those based on reflective principles) must also be carefully designed to preserve the resistive load required by the amplifier load network at the fundamental and harmonics. Diplexer technologies must be considered for this function especially in wideband switching amplifiers using wideband load networks that usually does not provide high harmonic rejection (20 dBc or less).

Acknowledgments

This work was partially supported by Spanish MEC funding (TEC2006-08210), Comunidad Autonoma de Madrid and Universidad Politecnica de Madrid.

References

1. T. Liang, J.A. Pla, P.H. Aaen and M. Mahalingam, “Equivalent-circuit Modeling and Verification of Metal-ceramic Packages for RF and Microwave Power Transistors,” IEEE Transactions on Microwave Theory and Techniques, Vol. 47, No. 6, June 1999, pp. 709-714.

2. F.J. Ortega-Gonzalez, J.M. Pardo-Martin, A. Gimeno-Martin and C. Benavente-Peces, “High Efficiency Broadband Power Amplifiers,” Microwave Journal, Vol. 51, February 2008, pp. 104-110.

3. N.O. Sokal, Scalable Analog Circuit Design, High-speed D/A Converters, RF Power Amplifiers, Kluwer Academic Publishers, Dordrecht, The Netherlands, 2002, Chapter “Class-E High-Efficiency RF/Microwave Power Amplifiers: Principles of Operation, Design Procedures and Experimental Verification.”

4. “Impedance-matched, Class F High-frequency Amplifier,” US Patent 5 146 178, September 8, 1992.

5. F.J. Ortega-Gonzalez, J.L. Jimenez-Martin and A. Asensio-Lopez, “Effects of Matching on RF Power Amplifiers Efficiency and Output Power,” Microwave Journal, Vol. 41, 1998, pp. 60-72.

6. L. Matthaei, L. Young and E.M.T. Jones, Microwave Filters, Impedance-Matching Networks and Coupling Structures, McGraw-Hill, New York, NY, 1964.

7. J. Sevick, Transmission Line Transformers, Noble Publishing, Norcross, GA, 2001.

8. D. Norman and H. Granberg, Radio Frequency Transistors - Principles and Practical Applications, Second Edition, Newne, Boston, MA, 2001.

9. B.W. Song, S.J. Kim and H.Y. Lee, “Vertical Integrated Transformer Using Bondwires for MMICs,” IEEE MTT-S International Microwave Symposium Digest, Boston, MA, June 2000, pp. 1341-1344.

10. H.L. Krauss, C.W. Bostian and F.H. Raab, Solid-state Radio Engineering, John Wiley and Sons Inc., New York, NY, 1980.