Commercially available 5 GHz WLAN transceivers—with the exception of power amplifiers (PA)—have recently been using advanced CMOS and SiGe BiCMOS technology.1 It is commonly believed that RFICs made with Si technology, especially CMOS technology, have the lowest cost and can be easily integrated with digital CMOS ICs to form a wireless system on a chip (SOC). In practice, CMOS transceivers integrated with digital CMOS ICs have been successfully demonstrated. However, it is still difficult to integrate the high power PA with the RF transceiver. There exist stand-alone high power CMOS PAs for cellular applications and low end SiGe PAs integrated with RF transceivers for 2.4 GHz WLAN applications. However, the strong coupling in the Si substrate prevents integrating the power amplifier with the RF transceiver. Thus, the commercially available PAs at 5 GHz are stand-alone and dominated by the GaAs technology.

As the scaling down of the CMOS device by deep submicron technology continues, the cost of fabrication becomes very high and the device operating voltage decreases. The integration of high power amplifiers with the SOC thus becomes more difficult. Moreover, the size of the RFICs does not follow the same scaling rule as the digital ICs. It is worthwhile to mention that the cost of research and development for the deep submicron CMOS IC design has increased dramatically due to the high cost of photo masks. In the past, the CMOS technology was very cost effective when compared with the 2 μm GaInP/GaAs HBT technology. As the channel length is shrinking, the R&D cost barrier of the deep submicron CMOS is much higher than that of the 2 μm GaInP/GaAs. The R&D cost of the 0.13 μm CMOS technology is 44 times the cost of the GaAs HBT technology.2

Although it is believed that the cost can be lowered down when the final product enters the mass production phase, the R&D cost barrier makes it very hard to finish a final product. The concept of the barrier for the CMOS R&D cost is illustrated in Figure 1. The Y-axis is the cost and the X-axis is the phase. On the top, the cost reduction of the digital circuit as CMOS is scaled down and is similar to a conventional diagram of the activation energy in chemistry. On the bottom, the diagram for the RFIC is shown when the size of the CMOS is scaled down. Only when the RF solution provider spends an enormous investment can the final product can be realized.

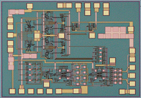

The GaInP/GaAs HBT technology needs only roughly 10 mask steps while CMOS technology has more than 20 mask steps. There already exists a six-inch GaAs fabrication as compared with the 12-inch Si fabrication. Thus, there is a chance that the production cost for GaAs HBT RF transceivers can be lower than that for CMOS RF transceivers. If the external GaInP/GaAs HBT PA is still unavoidable, it is straightforward to think of the possibility of integrating the whole transceiver including PAs in GaInP/GaAs HBT technology. RF transceivers contain many key components such as LNAs, mixers, wideband amplifiers and VCOs, as shown in Figure 2. In this article, many GaInP/GaAs HBT RFIC building blocks, except PAs for 5 GHz applications, are presented because 5 GHz GaInP/GaAs HBT PAs are commercially available. The goal is to build up a high performance GaAs RFIC single chip solution as shown in the figure.

The GaInP/GaAs HBT technology is suitable for the RFIC design. The semi-insulating substrate eliminates the notorious substrate coupling, and the RF performance can be improved. For instance, the LO substrate leakage of the Gilbert mixer can be eliminated. A state-of-the-art 2LO-to-RF isolation for the direct-conversion sub-harmonic Gilbert mixer has been achieved.3 The other advantage of the GaInP/GaAs HBT technology is its low 1/f noise corner. The CMOS transistor suffers from the 1/f noise because the inversion layer is located adjacent to the Si-SiO2 interface. Many dangling bonds (traps) existing in this interface make the device 1/f noise worse. On the other hand, the ledge of the HBT structure4 and the low DX centers of the GaInP/GaAs material make the 1/f noise of the HBT device minimal. The 1/f noise is very important for the RF circuits, especially for the oscillator and the direct-conversion mixer. The 1/f noise of the mixer can directly influence the output of the mixer, and the CMOS direct-conversion Gilbert mixer suffers from the worst 1/f noise.

The experimental results show that the GaInP/GaAs HBT has a 1/f noise corner as low as 400 Hz (depending on the bias condition and the emitter area), and several excellent direct-conversion sub-harmonic Gilbert mixers without 1/f noise are demonstrated. Moreover, a record high phase noise of the VCO was also demonstrated.5

LNA and Wideband Amplifiers

A cascode LNA with source inductive degeneration has been designed.6 The 2 μm GaInP/GaAs HBT LNA, without inter-stage matching, has a 14 dB power gain and a 2.37 dB noise figure at 5.2 GHz, while the 2 μm GaInP/GaAs HBT LNA, with inter-stage matching, has a 19.5 dB power gain and a 2.22 dB noise figure at 5.2 GHz. The circuit is biased at 3.6 V with a current consumption of 2.3 mA.

The shunt-series shunt-shunt dual-feedback wideband amplifier7,8 is the most popular topology for the RF gain building block. The design methodology of the wideband amplifier has been developed by identifying poles and zeros of the wideband amplifier.9-11 The shunt-series shunt-shunt wideband amplifier is a high speed Cherry-Hopper amplifier with a global shunt-series feedback. The experimental results show that a small-signal gain of 16 dB and a 3 dB bandwidth of 11.6 GHz with in-band input/output return losses less than 10 dB have been achieved. These values agreed well with those predicted from the analytic expressions that were derived for voltage gain, bandwidth, input and output impedances.

The design trade-off between gain bandwidth and matching bandwidth, using emitter capacitive gain peaking, has been demonstrated.12 Experimental results show that the power gain is 28 dB and the input/output return losses are better than 12 dB from DC to 6 GHz for the wideband amplifier without emitter capacitive gain peaking. The power and noise performance are very similar for both types of wideband amplifiers. Both circuits have an 8 dBm OP1dB and a 20 dBm OIP3 at 2.4 GHz. The noise figures of both designs are below 2.8 dB from 1 to 6 GHz. A simple down-converter consisting of the wideband amplifier used for LNA has been also demonstrated.13

Gilbert Down-Converters

The micromixer proposed by Gilbert14,15 is an ideal circuit topology for active RF mixer designs. The micromixer consists of a common-emitter single balanced mixer, a common-base single balanced mixer and a resistive degenerated current mirror. The micromixer can be viewed as an active balun that is able to generate differential signals from a single-ended RF input. Since the GaInP/GaAs HBT technology provides a semi-insulating substrate and a metal-plated ground, a microstrip line structure is suitable for signal propagation. The micromixer is good because the input resistors in this topology achieve the input impedance matching and thus the chip area is saved. A DC to 8 GHz wideband GaInP/GaAs HBT micromixer has been demonstrated.16 Its conversion gain is 11 dB using a resistive load and current injection technique.

The GaInP/GaAs HBT device has intrinsically an excellent 1/f noise performance. Consequently this technology is very suitable for direct-conversion mixers. Several direct-conversion sub-harmonic Gilbert mixers have been demonstrated.3,17,18 All of them have state-of-the-art 1/f noise performance caused by the device characteristic and record high port-to-port isolation resulting from the semi-insulating substrate. Figure 3 shows a photograph of the die of a direct-conversion sub-harmonic Gilbert down-converter with I/Q outputs.

The image signal suppression is a very important topic in RF receiver designs. The double quadrature Hartley down-converter with polyphase filters is a popular image rejection method for low IF receivers.19,20 The double quadrature down-converter consists of four Gilbert mixers and two passive four-section polyphase filters. Its die photograph is shown in Figure 4; the die size is 2 x 2.5 mm. The desired signal and the image signal can be separated after being mixed down by four Gilbert mixers. The IF polyphase filters can then filter out the desired signal from the image signal. A 5.2 GHz, 11 dB gain, IP1dB = –17 dBm and IIP3 = –10 dBm double quadrature Gilbert down-converter with polyphase filters21 has been demonstrated using GaInP/GaAs HBT technology. The image rejection ratio is better than 40 dB with the LO at 5.17 GHz and the IF is in the range of 15 to 40 MHz.

Another suitable solution to deal with the image signal is the Weaver architecture.22 A Weaver down-converter has been demonstrated using GaInP/GaAs HBT technology23 with some advantages, such as the semi-insulating substrate and accurate thin-film resistors. The Weaver system is a double-conversion image rejection heterodyne system, which requires no bandpass filters in the signal path and no quadrature networks. The Weaver down-converter has image rejection ratios of 48 and 44 dB when the RF frequency is 5.2 and 5.7 GHz, respectively. The integration level of this GaInP/GaAs IC is quite high and the IC contains 166 GaInP/GaAs HBTs. The die photograph of the Weaver down-converter is shown in Figure 5. The die size is 2 x 2.5 mm.

Gilbert Up-Converters

A miniature lumped-element rat-race hybrid24 and an LC current combiner are used in the LO port and the RF port of the up-conversion micromixer, respectively.25 The fully integrated micromixer has a conversion gain of 1 dB, an OP1dB of –10 dBm and an OIP3 of 2 dBm, when the input IF = 300 MHz, the LO = 4.9 GHz and the output RF = 5.2 GHz. The output RF return loss is 23 dB at 5.2 GHz and the IF input return loss is better than 25 dB for frequencies up to 8 GHz.

In addition, the operation principle and the analytic function of the LC current combiner, with the effect of the series resistor in an inductor, have been developed. The LC current combiner can be treated as a bandpass and passive current mirror load. Compared with low pass and active current mirror load, the LC current combiner has a better performance when the output frequency is increased. Therefore, the LC current combiner is an ideal topology for up-conversion mixer design.

An up-conversion micromixer with integrated VCO has also been demonstrated.26 A cross-coupled LC oscillator with an oscillation frequency of 4.3 GHz and a cascode buffer amplifier are also integrated on the same chip. The fully integrated up-conversion micromixer has a conversion gain of –2.5 dB, an OP1dB of –12.5 dBm and a 40 dB RF-to-IF isolation, when the input IF = 0.9 GHz and thus the output RF = 5.2 GHz. The IF input return loss is better than 25 dB for frequencies up to 6 GHz, while the RF output return loss is better than 12 dB for frequencies from 5.15 to 5.35 GHz.

VCO and Dividers

A GaInP/GaAs HBT quadrature VCO27 has also been implemented. A fully integrated GaInP/GaAs HBT quadrature VCO using a stacked-transformer LC tank has been demonstrated28 at 5.43 to 5.31 GHz with a low phase noise performance. The GaInP/GaAs HBT device has a small low frequency noise because of the low base resistance, the suppression of trap-related 1/f noise by the device passivation ledge over the extrinsic base surface and the absence of DX trap center in the GaInP material. A stacked transformer has the highest mutual coupling factor (close to one) between two spiral inductors29 and the GaAs semi-insulating substrate permits a high self-resonant frequency for the stacked transformer. The quadrature VCO at 5.38 GHz has a phase noise of –127.4 dBc/Hz at 1 MHz offset frequency, an output power of –4 dBm and a figure of merit (FOM) of –191 dBc/Hz.

A 4.9 GHz, transformer-based, super-harmonic VCO has been demonstrated5; its phase noise is –131 dBc/Hz at 1 MHz offset frequency. The state-of-the-art VCO has a figure of merit (FOM) of –198 dBc/Hz. A 5.7 GHz interpolative VCO,30 with a wide tuning range, has been demonstrated.31 The frequency tuning is achieved by interpolating two fixed oscillators instead of changing the tank capacitor. The demonstrated tuning range is 500 MHz. A 50 percent duty cycle divide-by-three GaInP/GaAs HBT prescaler has been demonstrated.32 The input frequency can be up to 1.7 GHz and the output singles have a 50 percent duty cycle.

Conclusion

Several key RFIC building blocks, including an LNA, a wideband amplifier, an up/down-conversion micromixer, a Hartley image rejection down-converter, a Weaver image rejection down-converter, VCOs and a divider have been designed and implemented using the 2 μm GaInP/GaAs HBT technology. The GaInP/GaAs HBT technology is suitable for RFIC design, and this work has demonstrated the possibility of a fully integrated RF transceiver.

Acknowledgments

This work is supported by the National Science Council of Taiwan, Republic of China, under contract numbers NSC 96-2752-E-009-001-PAE and NSC 95-2221-E-009-043-MY3, by the Ministry of Economic Affairs of Taiwan under contract number 95-EC-17-A-05-S1-020, and by the MoE ATU Program under contract number 95W803. The authors would like to thank the NDL RFTC group for the measurement support and the CIC for chip fabrications.

References

1. T.H. Lee, H. Samavati and H.R. Pategh, “5 GHz CMOS Wireless LANs,” IEEE Transactions on Microwave Theory and Techniques, Vol. 48, No. 2, February 2000, pp. 170–181.

2. M. Chang, “Foundry Future: Challenges in the 21st Century,” ISSCC 2007.

3. T.H. Wu, S.C. Tseng, C.C. Meng and G.W. Huang, “GaInP/GaAs HBT Sub-harmonic Gilbert Mixers Using Stacked-LO and Leveled-LO Topologies,” IEEE Transactions on Microwave Theory and Techniques, Vol. 55, No. 5, May 2007, pp. 880–889.

4. D. Costa and A. Khatibzadeh, “Use of Surface Passivation Ledge and Local Feedback to Reduce Amplitude Modulation Noise in AlGaAs/GaAs Heterojunction Bipolar Transistor,” IEEE Microwave and Wireless Components Letters, Vol. 4, No. 2, February 1994, pp. 45–47.

5. C.C. Meng, Y.W. Chang and S.C. Tseng, “4.9 GHz Low Phase Noise Transformer-based Super-harmonic-coupled GaInP/GaAs HBT QVCO,” IEEE Microwave and Wireless Components Letters, Vol. 16, No. 6, June 2006, pp. 339–341.

6. C.C. Meng and J.C. Jhong, “5.2 GHz GaInP/GaAs HBT Cascode LNA with 5.5 dB Gain Enhancement Using Inter-stage LC Matching,” Microwave and Optical Technology Letters, Vol. 48, No. 8, August 2006, pp. 1499–1501.

7. R.G. Meyer and R.A. Blauschild, “A 4-terminal Wideband Monolithic Amplifier,” IEEE Journal of Solid-State Circuits, Vol. 16, No. 6, December 1981, pp. 634–638.

8. C.D. Hull and G.B. Meyer, “Principles of Monolithic Wideband Feedback Amplifier Design,” International Journal on High Speed Electronics, Vol. 3, February 1992, pp. 53–93.

9. M.C. Chiang, S.S. Lu, C.C. Meng, S.A. Yu, S.C. Yang and Y.J. Chan, “Analysis, Design and Optimization of GaInP/GaAs HBT Matched-impedance Wideband Amplifiers with Multiple Feedback Loops,” IEEE Journal of Solid-State Circuits, Vol. 37, No. 6, June 2002, pp. 694–701.

10. S.S. Lu, C.C. Meng, T.W. Chen and H.C. Chen, “A Novel Interpretation of Transistor S-parameters by Poles and Zeros for RF IC Circuit Design,” IEEE Transactions on Microwave Theory and Techniques, Vol. 49, No. 2, February 2001, pp. 406–409.

11. S.S. Lu, C.C. Meng, T.W. Chen and H.C. Chen, “The Origin of the Kink Phenomenon of Transistor Scattering Parameter S22,” IEEE Transaction on Microwave Theory and Techniques, Vol. 49, No. 2, February 2001, pp. 333–340.

12. C.C. Meng, T.H. Wu and S.S. Lu, “28 dB Gain DC–6 GHz GaInP/GaAs HBT Wideband Amplifiers With and Without Emitter Capacitive Peaking,” 2002 European Gallium Arsenide and Other Semiconductors Application Symposium Digest, pp. 311–314.

13. T.H. Wu and C.C. Meng, “Inductorless Broadband RF Front-end Using 2 μm GaInP/GaAs HBT Technology,” 2007 IEEE MTT-S International Microwave Symposium Digest.

14. B. Gilbert, “The Micromixer: A Highly Linear Variant of the Gilbert Mixer Using a Bisymmetric Class-AB Input Stage,” IEEE Journal of Solid-State Circuits, Vol. 32, No. 9, September 1997, pp. 1412–1423.

15. J. Durec and E. Main, “A Linear Class AB Single-ended to Differential Transconverter Suitable for RF Circuits,” 1996 IEEE MTT-S International Microwave Symposium Digest, Vol. 2, pp. 1071–1074.

16. C.C. Meng, S.S. Lu, M.H. Chiang and H.C. Chen, “DC to 8 GHz 11 dB Gain Gilbert Micromixer Using GaInP/GaAs HBT Technology,” Electronics Letters, April 2003, pp. 637–638.

17. T.H. Wu and C.C. Meng, “10 GHz Highly Symmetrical Sub-harmonic Gilbert Mixer Using GaInP/GaAs HBT Technology,” IEEE Microwave and Wireless Component Letters, Vol. 17, No. 5, May 2007, pp. 370–372.

18. T.H. Wu, C.C. Meng and T.H. Wu, “5.7 GHz GaInP/GaAs HBT Sub-harmonic Gilbert Down-converter With the Octet-Phase LO Generator,” IEEE Electronics Letters, Vol. 42, No. 19, September 2006, pp. 1098–1099.

19. F. Behbahani, Y. Kishigami, J. Leete and A. Abidi, “CMOS Mixers and Polyphase Filters for Large Image Rejection,” IEEE Journal of Solid-State Circuits, Vol. 36, No. 6, June 2001, pp. 873–887.

20. J. Crols and M. Steyaert, “A Single Chip 900 MHz CMOS Receiver Front-end With a High Performance Low IF Topology,” IEEE Journal of Solid-State Circuits, Vol. 30, No. 12, December 1995, pp. 1483–1492.

21. C.C. Meng, D.W. Sung and G.W. Huang, “A 5.2 GHz GaInP/GaAs HBT Double Quadrature Down-converter With Polyphase Filters for 40 dB Image Rejection,” IEEE Microwave and Wireless Components Letters, Vol. 15, No. 2, Feburary 2005, pp. 59–61.

22. J.C. Rundell, J.J. Ou, T.B. Cho, G. Chien, F. Brianti, J.A. Weldon and P.R. Gray, “A 1.9 GHz Wideband IF Double Conversion CMOS Integrated Receiver for Cordless Telephone Applications,” IEEE Journal of Solid-State Circuits, Vol. 32, No. 12, December 1997, pp. 2071–1088.

23. T.H. Wu and C.C. Meng, “5.2/5.7 GHz 48 dB Image Rejection GaInP/GaAs HBT Weaver Down-converter Using LO Frequency Quadrupler,” IEEE Journal of Solid-State Circuits, Vol. 41, No. 11, November 2006, pp. 2468–2480.

24. S.J. Parisi, “180° Lumped Element Hybrid,” 1989 IEEE MTT-S International Microwave Symposium Digest, pp. 1243–1246.

25. C.C. Meng, T.H. Wu and M.C. Lin, “Compact 5.2 GHz GaInP/GaAs HBT Gilbert Up-converter Using Lumped Rat-race Hybrid and Current Combiner,” IEEE Microwave and Wireless Components Letters, Vol. 15, No. 10, October 2005, pp. 579–581.

26. C.C. Meng, S.K. Hsu, A.S. Peng, S.Y. Wen and G.W. Huang, “A Fully Integrated 5.2 GHz GaInP/GaAs HBT Up-conversion Micromixer With Output LC Current Combiner and Oscillator,” 2003 IEEE MTT-S International Microwave Symposium Digest, Vol. 1, pp. A205–A208.

27. P. Andreani, “A Low Phase Noise, Low Phase Error, 1.8 GHz Quadrature CMOS VCO,” Proceedings of the 2002 ISSCC, pp. 290–291.

28. C.C. Meng, C.H. Chen, Y.W. Chang and G.W. Huang, “5.4 GHz–127 dBc/Hz at 1 MHz GaInP/GaAs HBT Quadrature VCO Using Stacked Transformers,” Electronics Letters, Vol. 41, No. 16, August 2005, pp. 906–908.

29. M. Zannoth, B. Kolb, J. Fenk and R. Weigel, “A Fully Integrated VCO at 2 GHz,” IEEE Journal of Solid-State Circuits, Vol. 33, No. 12, December 1998, pp. 1987–1991.

30. N.M. Nguyen and R.G. Meyer, “A 1.8 GHz Monolithic LC Voltage-controlled Oscillator,” IEEE Journal of Solid-State Circuits, Vol. 27, No. 3, March 1992, pp. 444–450.

31. S.A. Yu, C.C. Meng and S.S. Lu, “A 5.7 GHz Interpolative VCO Using GaInP/GaAs HBT Technology,” IEEE Microwave and Wireless Components Letters, Vol. 12 No. 2, February 2002, pp. 37–38.

32. S.C. Tseng, C.C. Meng and W.Y., “SSH and SHH GaInP/GaAs HBT Divide-by-3 Prescalers With True 50% Duty,” Electronics Letters, Vol. 42, No. 14, 2006.

Chin-Chun Meng received his BS degree in electrical engineering from National Taiwan University, Taipei, Taiwan, ROC, in 1985, and his PhD degree in electrical engineering from the University of California at Los Angeles (UCLA) in 1992. He then joined the Hewlett Packard Component Group, Santa Clara, CA, in 1993 as a member of the technical staff. He is now an associate professor in the department of communication engineering at National Chiao Tung University, HsinChu, Taiwan, ROC. His current research interests include radio frequency integrated circuits (RFIC), high frequency circuit and high speed devices.

Tzung-Han Wu received his BS and MS degrees in electrical engineering from National Chung-Hsing University, Taichung, Taiwan, ROC, in 2001 and 2003, respectively. He is currently working toward his PhD degree in the department of communication engineering at National Chiao Tung University, Hsinchu, Taiwan, ROC. His current research interests include RFICs and MMICs.