Wireless systems-on-a-chip (SoC) have seen very high levels of integration in the last few years because the market is demanding reduced cost and low component count. Further to this trend, the integration of multiple standards has been introduced into the SoC. This integration strategy has caused superheterodyne receiver architectures to fall out of favor, thereby sacrificing performance. This article promotes analog front ends that are suitable for integrating into a SoC to relieve requirements on standard digital techniques and A/D converters.

A new technology called a “Sampling IF Filter” (SIF) will be discussed and it will be shown how it is more suitable for integrating filters onto a SoC. This is an enabling technology, which will re-popularize the superheterodyne receiver architecture for wireless SoC applications. How this technology can facilitate receiver design in general will also be discussed. To place the sampling IF filter in context, the current status of on-chip filters will be reviewed.

Existing Filter Technologies

Three well-known filter technologies have been used for integrating IF filters on chip. The oldest is the active resistor capacitor (RC) filters. Another old technology for on-chip IF filters is the switched capacitor (SC) filter. The transconductor capacitor (gm–C) filter has been used in more recent radio designs. Each approach has its own strengths and weaknesses, which often makes selection of the most appropriate approach difficult.

Active Resistor Capacitor Filters

These are typically constructed from bi-quad sections, where each bi-quad has a network of resistors, capacitors and op-amps. The bi-quad sections are then cascaded to produce the desired filter response. The major issue with this approach is that both the resistor and capacitor tolerances on-chip are not tight enough. This can yield a large range of RC time constants and consequently a large error in the frequency response. On-chip, the ratios of like devices such as resistor-to-resistor and capacitor-to-capacitor can be better controlled within a few percent, but the variations in time constants can vary by ±30 percent in a typical process. In an attempt to improve the frequency accuracy, SC filters were introduced.

SC Filters

SC filters are constructed by substituting the resistors in an active RC filter with switches and capacitors. These SC filters have very precisely defined passband characteristics, because the time constants associated with the frequency response depend only on the capacitor ratios and the clock frequency. A serious drawback with using SC filters in an IF stage is the danger of aliasing interfering signals. Using SC filters for an IF filter can result in noise problems because of the difficulty in obtaining low noise samples of the input signal. Since the op-amps used in SC filters must have greater bandwidth than the signal they are processing, they tend to consume too much power for high data rate applications that are battery operated. The noise problem can be solved by using larger capacitors, although this worsens the problems with op-amp bandwidth. These noise and aliasing issues are further compounded in a low power, low clock-rate system. In some ways, these filters are superior to gm–C filters (see below) in that they are not sensitive to variations in temperature and process. This means that a working SC filter can be designed to achieve first silicon success, unlike the gm–C filters that usually require several passes.

gm–C Filters

gm–C filters are constructed by replacing the inductor in an LC filter with a capacitor and a gyrator made with a transconductance amplifier. Typically, gm–C filters provide lower noise and lower power in a given process than SC filters but suffer in two problem areas where SC filters perform better. The first problem is that, typically, a trade-off is required between power and linearity. The second is the trade-off between linearity and bandwidth. Any attempts at improving linearity force the designer to use multi-transistor gm elements that reduce the available bandwidth by introducing extra parasitic poles. Since the time constants in a gm–C filter depend on two independent process variables (gm and C), they tend to have poorly controlled passband frequency response characteristics, unless a process calibration loop is included. This poorly controlled frequency response can adversely affect the chip yield and result in a re-spin of the chip to produce the desired transfer function (the transfer function of a filter is the gain or attenuation versus the input frequency).

Sampling IF Filters

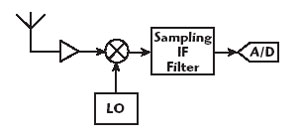

This article highlights a new filter technology called “Sampling IF Filter” (SIF) (see Figure 1). This technology combines the low power, low noise properties of a gm-C filter with the precisely controlled passband and process independence of a SC filter. The product has an automatic gain control (AGC) stage, an anti-alias filter, a channel select filter and a sampler in a single unit. This low power technique can be part of an integration strategy. Currently, designs of on-chip filters are up to 900 MHz and can be used to replace an off-chip SAW filter. As the technology lends itself to being field programmable, a sampling IF filter can replace several off-chip filters. The sampling IF filter is also process and temperature tolerant. This can help in lowering costs at the foundry as it reduces the number of fabrication runs and, because of this, manufacturers can get the product to market faster, enabling them to engage customers early on. Further, as the channel selection filtering is performed before the A/D converter as part of the sampler, this method substantially reduces both speed and resolution requirements specified for the A/D converter (see Figure 2). In turn, this provides additional power savings by allowing the use of a much simpler A/D converter. Without filtering before the A/D, the bandwidth and dynamic range need to accommodate both the signal and any interfering signals. By sampling and filtering prior to the digital stage, the bandwidth and the dynamic range of the A/D can now be reduced. As the requirements for the A/D have been reduced, the A/D is no longer a high performance component and can easily be integrated as an add-on to the sampling IF filter. As stated earlier, the disadvantages of SC filters are that they are noisy and have high power consumption, although their transfer functions are stable over temperature and process variations. It was stated previously that gm–C filters offered low power consumption, but their drawback is that they are less stable over the same variations. The sampling IF filter presented here represents a valuable breakthrough, because it is superior to the strengths of both of these filter technologies.

Fig. 1 Sampling IF filter.

Fig. 2 Reduced dynamic range and bandwidth.

Field Programmable

The sampling IF filters can be designed for high RF image rejection without any requirement for digital correction techniques. Sampling IF filters are very versatile and can be applied to receivers in WiMAX 802.16, Bluetooth, GSM, WLAN (Wi-Fi) 802.11a, 802.11b, 802.11g, 802.11h and 802.11n, software-defined radios (SDR), multi-mode radios, pagers, and cable modem products. In multi-mode radio applications, there is a great advantage to making the sampling IF filter programmable, as all off-chip filters can now be integrated.

Process and Temperature Independence

Changes in process or temperature in an RC filter change the time constants, which change the transfer function, making it difficult to achieve a higher order filter. In a sampling IF filter, process and temperature variation will only change the gain, which has no effect on the transfer function because the SIF is embedded inside an AGC loop, which will correct any gain error. With this last gain error corrected, the SIF is completely insensitive to any process and temperature variations. Automatic gain control can be added at any stage of the sampling IF filter. The AGC loops are digital and therefore can be very fast. Packet type architectures usually require a fast AGC because it is necessary that the AGC level be set before the training sequence or packet information becomes available for demodulation.

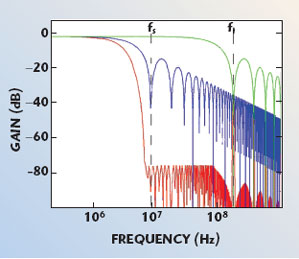

The red line, shown in Figure 3, represents the response of the filter with no process or temperature variations included. The blue lines represent the effects of component mismatch and all other circuit and temperature variations. The frequency response of the passband is unaffected by any process or temperature variations. The stopband attenuation of the aliases is also maintained even with component mismatch. The sampling IF filter technique is less susceptible to process variations than either of the two incumbent on-chip filter technologies.

Fig. 3 Effect of mismatch.

The SIF filter is composed of different stages that can be assembled for the desired application. Some example stages of a sampling IF filter that can be used are discussed below.

The Common Anti-alias Filter Building Block

A common anti-alias filter building block, used in sampling intermediate frequency filters, is the finite impulse response (FIR) filter. This filter function is produced by the continuous time integration of the incoming signal over a minimum integration interval, Ti. This integrate-and-dump filter has a transfer function of sinc (f /fi), where fi = 1/Ti is the integration frequency. The overall SIF filter has a passband B (see Figure 4). Signals that will alias into this passband are those signals that will occur at frequencies that are multiples of fi. After sampling, the amount of rejection for these signals is approximately 20 log (fi /B). When the system architecture requires continuous-time pre-filtering in addition to the common sampling IF filter attenuation of 20 log (fi /B), this pre-filtering can be done with passive elements or gm–C filters. Here is a case where low tolerance gm–C filters can be useful, because precision in the filter transfer function is not required. The only requirement is to supply substantial attenuation at frequencies close to fi and its multiples.

Fig. 4 Frequencies and bandwidth in the common anti-alias filter building block.

Enhanced Anti-alias Filter by Extended Integration Intervals

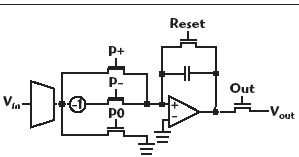

By integrating over several periods of fi, to produce a lower output frequency, fs, the common anti-alias filter can be made more selective. This enhanced selectivity can be created either at DC, or, in the case of poly-phase filters, at certain discrete intermediate frequencies. For poly-phase filters, the center frequency is set by FcAA = N1 (fi/N2), where FcAA is the center frequency of the common anti-alias filter, N1 is a number used to select a channel or band of frequencies and N2 is the number of phases in the poly-phase filter. If N1 is made programmable and N2 is greater than four, this will give some flexibility in the range of intermediate frequencies. Making fi programmable further increases the flexibility of the design to create multiple transfer functions that can be applied to various wireless applications. Figure 5 shows a simplified circuit diagram of the enhanced anti-alias filter. Typically, this method employs differential circuitry although the figure shows a single ended version to simplify the demonstration. In a differential circuit, the gain of –1 shown can be implemented by crossing a pair of wires to invert the polarity of the current. Figure 6 shows some possibilities of different transfer functions that can be created by using this type of enhanced anti-alias filter. By manipulating N1 and N2, the useful bandwidth B can be moved from DC to a range of IF frequencies.

Fig. 5 Block diagram of an enhanced anti-alias filter.

Fig. 6 Frequencies and bandwidth.

Enhanced Anti-alias Filter by Extended Integration Intervals ad Resistor-weighted Tap Coefficients

While the enhanced anti-alias filter provides better anti-alias attenuation than the minimal anti-alias filter, a resistor tap coefficient can be used to provide better attenuation at multiples of the sampling frequency fs. One of the reasons for having greater attenuation at multiples of fs is to prevent aliasing when the output of the filter is sampled to the next stage.

This further enhanced anti-alias filter provides additional attenuation between the frequencies fs and fi. An example is shown in Figure 7. In this example, the green line shows the built-in common anti-alias filter discussed previously, with its first notch at fi. The notch occurs at 160 MHz because the integration interval is 6.25 ns. The blue line shows the transfer function resulting from extending the integration interval, as discussed in the previous section, to 16 integration intervals or 100 ns. This gives an output sampling frequency of 10 MHz and a deep notch at 10 MHz. By using 62 resistor-weighted tap coefficients, the transfer function can be created as shown by the red line. The increased attenuation, shown by the red line, is necessary to prevent signals from 10 MHz to fi from aliasing into the desired signal bandwidth B. The further enhanced anti-alias filter can be created at DC or any frequency up to fi/2. The impulse response is finite (FIR) and has a linear phase. To save area and power when higher levels of filtering are required, additional stages can be added to the anti-alias filter. This allows for the sampling frequency to be reduced in smaller steps with sufficient anti-alias filtering at each stage. This lower sampling frequency will save power in subsequent stages of the filter, the A/D converter and in the Digital Signal Processor (DSP). The idea is to lower the sampling frequency, which in turn lowers the number of tap coefficients required, while achieving the same desired filtering. A benefit of using the sampling IF filter is that filtering is performed on the analog side of the system instead of after the A/D.

Fig. 7 Frequencies and bandwidth.

Other IF Stages

One advantage of any sub-sampled technique is that a desired alias can be selected to down-convert to baseband. The advantage of the sampling IF filter technique is that other aliases can be easily rejected while not disturbing the desired alias. Previously, there was a high cost to down-conversion and filtering of IF stages. However, with this unique technique, IF down-conversion occurs as part of the sampling IF filter. As there is no longer an added cost for these down-conversion stages, the architectures can be re-examined to gain a competitive advantage. A process-independent technique for integrating IF stages on chip will be discussed, using a sampling IF filter. This technique permits the integration of multiple IF stages on-chip enabling designers to migrate back to superheterodyne receiver architectures. The sampling IF filter technique offers further improvements by allowing for significant relaxation of the RF front-end requirements by using a higher IF frequency. These relaxed RF front-end requirements can be exploited for further cost reductions. Before looking at superheterodynes, a review of single IF receivers and zero IF receivers is presented.

A Review of Receiver Architectures

To fully appreciate the value of the sampling IF filter, the commonly used SoC receiver architectures will be reviewed and their strengths and weaknesses discussed. Several years ago, as SoC integration began, low noise amplifiers, mixers and many of the basic components were integrated. However, there were still plenty of off-chip components, including frequency synthesizers, voltage-controlled oscillators, power amplifiers and filters. Eventually many of these were integrated leaving just the filters to integrate. Finally, when the industry required on-chip filters, there was no available filter technology for high frequencies. This forced the use of alternative architectures that employed low frequency filters that could be constructed from the types discussed earlier.

Single IF Receivers

A simplified block diagram of a single IF or heterodyne receiver is shown in Figure 8. A band-select filter removes any out-of-band signals from the incoming RF signal received by the antenna. An image-reject bandpass filter (BPF) removes the image frequency from the LNA output prior to down-conversion to the desired intermediate frequency by the mixer. Typically, a crystal or SAW filter anti-aliases to allow A/D conversion, then the rest of the receiver is digital. Single-IF architectures have a trade-off between sensitivity and selectivity. Sensitivity relates to the ability of the receiver to distinguish extremely weak signals that are very close to the ambient noise floor. Selectivity is the ability to distinguish these weak signals from other interfering signals that are close in frequency. The potential source of interfering signals can be external or unintentionally generated by other parts of the system. If the IF is high, then the image appears far away from the desired signal band and can easily be suppressed by a bandpass filter. However, the high IF cannot be fed directly into the A/D converters for digital demodulation. If the IF is low, then channel selection becomes easier, but now proper suppression of the image becomes harder to achieve, because a high Q-factor RF selection filter is needed, which is very difficult to design (Q being the ratio of the center frequency to the 3 dB bandwidth). The use of an image-reject mixer can theoretically reduce the selectivity requirements of the image-reject filter, but this becomes difficult with conventional techniques if more than 40 dB of image rejection is required from the mixer.

Fig. 8 Single IF receiver.

Zero IF Receivers

A simplified block diagram of a homodyne receiver is shown in Figure 9. The zero IF (ZIF) radio receiver uses a direct-conversion architecture. This means that it utilizes a single mixer stage and avoids any costly IF stages. In this architecture, the received signal is frequency converted directly to baseband. Therefore, a low pass filter is utilized to remove any out of band signals, thus avoiding the requirement for high Q bandpass filters. Many ZIF radio designs also integrate the low noise amplifier (LNA), voltage-controlled oscillator (VCO) and the baseband filters on a single die. Single-chip ZIF transceivers have been used in cellular applications and are currently being introduced in WLAN radio designs.

Fig. 9 Zero IF receiver architecture.

Some disadvantages of the ZIF receiver architecture are DC offset and flicker noise. DC offset is generated by any LO leakage entering the receive path. This LO leakage mixes with itself creating a DC component in the signal chain that affects the receiver performance and can saturate the RF stages. Preventing this leakage requires careful attention to the layout of the IC to prevent coupling of the LO or other interfering signals through substrate coupling or mutual inductance of supply lines. Flicker noise, or 1/f noise, is a low frequency noise generated in the transistors, which can corrupt signals in the receiver chain. Flicker noise is a major concern with ZIF architectures, because the desired signal is down-converted to the same low frequency where transistors have their highest noise level. This problem is most severe in pure CMOS processes. Performance in narrowband applications suffers greatly when ZIF architectures are applied. Another issue with ZIF receivers is that most of the gain is at a single baseband frequency in the receive path. Having a high gain at a single frequency can cause instability in the amplifier.

Superheterodyne Receivers

Superheterodyne receivers were once the workhorses of microwave receiving systems (see Figure 10). They were the most popular and the highest quality receiver architecture for many years. Recently, systems architects have moved away from two-stage superheterodyne receivers in favor of single intermediate frequency (IF) or direct conversion architectures (ZIF). The main reason for reducing the number of IF stages in a SoC chip has been to avoid off-chip filters and their drivers in order to obtain a lower cost, power and pin count. The alternative of integrating the off-chip filters was not viable because of the lack of technology for on-chip high IF filters with repeatable transfer functions.

Fig. 10 Superheterodyne receiver architecture.

Advantages of the Superheterodyne

Superheterodyne is usually the preferred method of designing wireless communications receivers. This architecture utilizes a dual down-conversion process having two separate IF frequencies. These two separate IF mixer stages can simplify the filters at each stage. They also eliminate the conflict that exists between sensitivity and selectivity when using single IF or ZIF architectures. Having a high frequency first IF and hence an image frequency that is far away from the RF frequency means that a simple RF filter network is sufficient to reject interfering signals at the image frequency. Similarly, the first IF stage filter can also be a simple filter network as its function is only to eliminate image frequencies from the second LO. The second IF filter is required for channel selection only and operates at a low frequency. This means that high selectivity can be achieved with low Q components.

This architecture achieves more than simplifying the filters; it also improves the total system noise figure because simpler filter stages have less insertion loss. This improvement in system noise figure can typically be several dB. In a multi-mode receiver, the improvement in noise budget allows for more creativity on the part of the designer. For example, this improvement could be transferred to the Tx/Rx switching network, meaning that cost improvements could then be realized in both the filters and the switch. In a superheterodyne, this improvement in noise figure and sensitivity is achieved without any compromise in selectivity.

Disadvantages of the Superheterodyne

Careful selection on the frequency plan ensures that the system will be optimized for selectivity and sensitivity. However, the available off-chip filter technologies usually dictate the frequency plan. Designers are constantly scouring the market for low cost and easily available filters, and build their systems around the frequencies of these components. This off-chip conflict is more restrictive when one tries to integrate the filters on-chip.

On-chip SIF-based Super-heterodyne Architecture

An on-chip SIF-based superheterodyne architecture is shown in Figure 11. In this architecture, the SIF1 and SIF2 stages each provide a filter and sampled output. The sampling at the output of each stage uses aliasing to down-convert a desired frequency band centered at fc. Figure 12 shows the SIF first stage transfer function, where fc =113 MHz and fs = 50 MHz. This causes the frequency components of the input signal near 113 MHz to alias to 13 MHz at the output of the first sampling IF filter stage. The frequencies near fc are passed by the filter. Frequencies near fc ± kfs, where k ≠ 0, which would also alias to 13 MHz at the filter output, are highly attenuated. This way, only the desired alias of the input signal is selected for down-conversion by sampling (aliasing).

Fig. 11 SIF-based superheterodyne architecture.

Fig. 12 Bandpass SIF transfer function for a superheterodyne first IF stage.

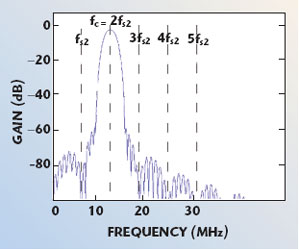

Figure 13 shows the second stage transfer function, where fc = 13 MHz and fs2 = 6.5 MHz. As a result, the 13 MHz output from the first stage filter is further filtered and down-converted to a baseband output having in-phase and quadrature components for A/D conversion and further digital processing. In summary, the on-chip SIF-based superheterodyne architecture has all of the advantages previously enjoyed by the traditional superheterodyne, while permitting on-chip filter integration.

Fig. 13 Bandpass SIF transfer function for a superheterodyne second IF stage.

Programmable Filter Transfer Functions

When the specifications call for different data bandwidths or data rates, the programmable FIR filter can create several predetermined filter transfer functions on the fly (see Figure 14). The blue frequency response represents the first enhanced anti-alias filter stage. This was the red line in the figure shown in the enhanced anti-alias filter by extended integration intervals and resistor-weighted tap coefficients section. Any one of the other three frequency responses could be programmed into a second enhanced anti-alias filter stage.

Fig. 14 Examples of programmable FIR filters.

The examples shown are used to indicate the variety of filter options that are available in a single stage. Each filter transfer function can have its own bandwidth, stopband attenuation and shape factor as part of each enhanced anti-alias filter stage. As the filtering requirements of the filter become more demanding on all three parameters, additional enhanced anti-alias filter stages need to be added. The three additional transfer function examples were chosen to be suitable for three different sampling frequencies at the output of the programmable FIR stage. To recap, the blue line is a single-stage enhanced anti-alias filter and the remaining three lines are made from a two-stage enhanced anti-alias filter. The parameters for the programmable filter are shown in Table 1.

Figure 15 shows three transfer functions of a programmable enhanced anti-alias filter. In this case, the anti-alias filter is a bandpass filter selecting the desired alias. This example highlights how each stage of an anti-alias filter can have programmable transfer functions.

Fig. 15 Programmable FIR transfer functions.

Conclusion

This article has shown that a sampling IF filter is a viable alternative to both SC and gm–C filters, because of its advantages in power consumption and process/temperature tolerance. When compared to an SC filter, this technique exhibits lower noise, while avoiding the aliasing problems and is more stable over process and temperature than a gm-C filter. Eliminating an AGC stage and reducing the bandwidth and resolution requirements of the A/D and digital processing realize further power savings. Superheterodyne wireless architectures are once again a viable option for the system designer due to the unique enabling capabilities of the sampling IF filter.