The technique of directing an antenna electronically rather than mechanically has been used for quite a number of years in the military domain and more recently for space applications. The numerous advantages of this technique, including lack of mechanical parts, small sized and lightweight antennas, fast positioning, beam agility, etc., has also lead to the adoption of the electronically steerable antenna or phased-array antenna to other applications. These include such diverse applications as weather radars, light radars for security, control and professional applications, radio-astronomy and in-car entertainment via satellite links.

The technique of directing an antenna electronically rather than mechanically has been used for quite a number of years in the military domain and more recently for space applications. The numerous advantages of this technique, including lack of mechanical parts, small sized and lightweight antennas, fast positioning, beam agility, etc., has also lead to the adoption of the electronically steerable antenna or phased-array antenna to other applications. These include such diverse applications as weather radars, light radars for security, control and professional applications, radio-astronomy and in-car entertainment via satellite links.

The technique is based on providing a correctly phased and dimensioned signal at each of the antenna dipoles forming the phased-array antenna. For this, digital phase shifters and attenuators are required along with low noise amplifiers and power amplifiers, while commutation between the transmit and receive modes is achieved by the use of RF switches.

GaAs MMICs have dominated these applications because of their superior performance. Previous generation systems have used individual MMICs for each of the functions (phase shifter, attenuator, gain block, LNA). However, to reduce size, manufacturing cost and weight, and to improve the cost effectiveness of the module, it is now necessary to move to fully integrated MMICs that include most or all of the above RF functions.

Integrated Solution

A typical block diagram is shown in Figure 1, where the three-port MMIC has a common port and receive/transmit ports that are configured with the on-chip RF switches. All ports are matched to 50 Ω in all configurations. The low noise and power amplifiers are separate MMICs, which provide maximum performance while maintaining an optimum level of integration and flexibility. The positioning of the gain blocks in the system depends on the overall requirement in terms of linearity, output power, noise figure and power consumption.

To address these requirements OMMIC has developed the CGY2175AUH (Control Functions) and CGY2178UH (LNA), which are standard products that have been designed for phased-array applications in C-band (4.5 to 6.5 GHz). Both are manufactured using the company’s ED02AH 0.18 μm PHEMT GaAs technology that provides excellent noise figure for the LNA, high gain and linearity for amplifiers, and good isolation for the switches, along with low loss for the phase shifters and attenuator.

Digital Interfacing

While classic D-mode GaAs technologies can provide solutions to the RF part of the control function MMIC, there is still the problem of interfacing to this MMIC, that is, providing the digital signals that will control the attenuator and phase shifter and possibly the switches. With a classic parallel interface, a MMIC with 6-bit phase shifting and 6-bit attenuation will require a minimum of 12 bits and up to 24 bits of parallel data with one bonding pad per bit, together with additional bonding pads for switch control, DC supply and RF interfacing.

These constraints make such a MMIC impractical for measurements, requiring many bonding wires, and would likely increase the size of the module compared to discrete solutions due to the need to get the large number of interfacing lines to the MMIC.

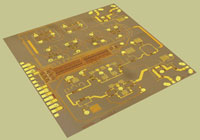

However, the solution considered here uses on-chip serial in, parallel out (SIPO) conversion that eliminates the requirement for a large number of bonding pads. The digital interfacing of the CGY2175AUH requires only three bonding pads for the digital interface : one for the Serial Data, one for the Clock and one for Latch Enable. The MMIC buffers then latch the data into on-chip registers where it is stored and used to control the state of the phase shifters and attenuators. The data that has been clocked through the registers is also buffered, is available at a bonding pad and can be used to further simplify the system architecture by allowing the cascading of a number of MMICs controlled by the same serial data stream. Figure 2 shows a detailed photograph of the digital portion of the CGY2175AUH.

The RF switch is actuated by a separate, buffered, control line to allow very high speed switching between the transmit and receive modes (10 ns). However, this could also be integrated into the serial data for other applications. Also, the clocking speed capability of the SIPO is over 100 MHz.

The Technology

The integration of the digital function with the RF circuits on the same MMIC is key to obtaining a highly integrated solution and to simplifying the interfacing to the MMIC, thereby reducing overall size and complexity, and obtaining a cost-effective solution.

To address these issues OMMIC’s ED02AH commercial foundry process combines a high performance (ft > 60 GHz) PHEMT depletion mode (negative Vt) transistor with an enhancement mode (positive Vt) transistor in the same integrated circuit. The depletion mode transistor is ideal for the RF functions, while the positive voltage only enhancement transistor can be used to make dense, low power consumption, robust and high yield digital circuits.

This technology, which is fully released and utilized for space flight level equipment, is used from 1 GHz to over 40 GHz and particularly for the C-band CGY2175AUH. The technology uses gold bonding pads and backside metallization and is fully protected with silicon nitride passivation to obtain the highest level of reliability.

Circuit Performance

The CGY2175AUH is a high performance three-port, 6-bit core chip GaAs MMIC operating in the C-band. It includes a 6-bit phase shifter, a 6-bit attenuator and T/R switch. As has been mentioned, the on-chip series in, parallel out conversion of the control data minimizes the number of bonding pads and greatly simplifies the use of the CGY2175AUH compared to other devices without this capability.

A separate on-chip high speed buffer allows a very fast 10 ns switching time between transmit and receive modes. The total power consumption of the MMIC, including Schmidt triggers for signal integrity, buffering, latches and level shifting is less than 100 mW. Furthermore, the MMIC is less than 18 mm2 and is delivered as a tested, inspected known good die (KGD).

The CGY2175AUH has a phase shifting range of 0° to 360° and an attenuation setting range of 31.5 dB. It covers the frequency range from 4.5 to 6.5 GHz.

The loss between input and output pads is typically 11.5 dB and the input and output matching (any port, any state) is better than –14 dB. Significantly, the phase and attenuation errors are very small: 1.5° and 0.2 dB, respectively (RMS values).

The phase setting and amplitude setting errors are also very good and are typically better than ±3° and –0.2 to +0.7 dB, respectively. The performance of the MMIC at 5.4 GHz is shown in Figures 3 and 4.

A key consideration is to achieve good RF isolation on the chip so as to isolate the transmit/receive channels and prevent cross talk on the chip that would introduce errors, particularly for the high attenuation levels.

The CGY2178AUH satisfies these criteria as the isolation of the switch is typically better than 40 dB and the error on amplitude and phase remains good even with the full 31.5 dB of attenuation setting (see Figure 4). The worst-case output 1 dB compression point is better than 20 dBm for the nominal attenuation setting.

The CGY2178UH is a high gain, low noise figure MMIC amplifier designed for use with the manufacturer’s integrated core chip MMIC family or as a general purpose low noise amplifier for C-band applications.

The device has all biasing, decoupling and output matching networks on chip, yet uses a very simple external matching circuit to provide good input matching (≤ –15 dB) and low noise figure (typically 1 dB) between 5 and 6 GHz, as shown in Figure 5.

The on-chip output matching network gives a better than ≤ –15 dB match. The use of the advanced 0.18 mm gate length PHEMT process contributes to the very low noise figure, along with very high gain (typically 30 dB) and low power consumption (40 mA at 3 V) in a small surface (1.5 X 1.4 mm). The output 1 dB compression point is of the order of 15 dBm.

Conclusion

High integration alone in a MMIC is not the solution to obtaining higher performance circuits. It is also necessary to simplify the use of the IC. In the case of the CGY2175AUH the inclusion of an on-chip digital circuit and the SIPO function, while at the same time integrating several RF functions (the switches, phase shifter and attenuator), has led to the size-performance-cost-improvement that is required for today’s Electronically Steerable Antennas.

As for the associated LNA—the CGY2178UH—the good noise figure (1 dB) for C-band applications is achieved by using a very simple, small external matching circuit. In this case the combination of the integrated MMIC with an off-chip network produces not only a very high performance design but also a very robust one that can be optimized in a particular bandwidth if required.

These devices can also be used as building blocks for specific custom designs where, for example, on-chip amplification is added to the Control Function MMIC and the SIPO function is expanded to include separate on-chip registers for the transmit and receive settings of the phase shifter and attenuator.

OMMIC,

Paris, France

Tel: +33 (0)1 45 10 69 22,

Fax: +33 (0)1 45 10 69 53,

e-mail: information@ommic.com; web site: www.ommic.com.