Finally, FPGAs incorporated into SDRs, enable both waveform storage and triggering. This enables these products to store predefined radar waveforms for different types of radar techniques and activate the transmission of these waveforms using external triggers connected to the FPGA within the SDR. This simplifies the overall architecture of a radar system and enables greater performance in a smaller footprint than alternative architectures.

Figure 4 Cyan commercial off-the-shelf (COTS) SDR and FPGA solution.

Figure 3 shows a representative functional block diagram for a radar system along with where Per Vices SDR platform solutions can add value. Figure 4 shows the Per Vices Cyan SDR that can be used in radar, EW or military communications applications. This platform provides simultaneous support for up to 16 fully independent transmit or receive radio channels. Each of these channels has 1 GHz of RF bandwidth with support for up to 3 GHz of bandwidth and up to 16-bit converters. The Cyan platform can tune from near DC to 18 GHz. The digital throughput includes four 40GBASE-R qSFP ports to receive and transmit radio data and this capability can be upgraded to four 100GBASE-R. The complexity and functionality of this platform hint at the benefits that SDR, coupled with FPGAs add to active electronically scanned array radars with many antenna elements.

Benefits of FPGAs in SDRs for EW

Flexibility is critical in EW. FPGAs can be programmed to perform a wide range of signal processing tasks and can be reprogrammed on the fly to adapt to changing requirements to meet these flexibility needs. This means that SDRs with FPGAs can easily accommodate new signal processing algorithms and modulation schemes, making them suitable for a broad range of EW applications.

FPGAs can process large amounts of data quickly. This is critical in EW applications, as this capability enables rapid detection, analysis and response to threats in the electromagnetic spectrum. The high speed processing capabilities of FPGAs make them an ideal choice for complex signal processing tasks inherent in EW applications. The ability to support real-time signal processing of vast amounts of data at high speeds makes this architecture invaluable in EW applications.

The ability to process large amounts of data is not the only benefit of FPGAs for EW systems. There is a need to acquire and process the data quickly, so low latency is another important characteristic of FPGAs. Latency refers to the time delay between the input signal and the output response. In EW applications, low latency enables the system to respond quickly to threats in the electromagnetic spectrum. With FPGAs, SDRs can achieve extremely low latency in signal processing, making them an ideal choice for high speed applications in electronic attack, protection and support.

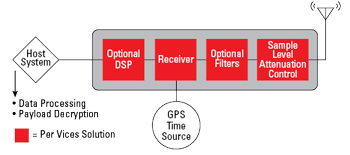

Figure 5 Representative EW system receiver block diagram showing the Per Vices solution.

FPGAs offer high performance computing capabilities, including filters, decimation and interpolation. This makes FPGAs an ideal choice for the complex algorithms and computations required in EW applications. With their parallel processing capabilities, FPGAs can perform multiple operations simultaneously, enabling them to handle complex computations quickly and efficiently. This allows this architecture to be used for all elements of EW, including electronic attack, electronic protection and electronic support, where real-time processing of complex algorithms is required for rapid detection and response to threats. Implemented properly, the FPGA and SDR combination can create significant tactical advantages on the battlefield.

All the above benefits are amplified by the fact that FPGAs can significantly reduce power consumption in SDRs for EW applications. Unlike traditional processors, FPGAs consume power only when they are performing computations. This means that they consume less power than traditional processors, making them a good choice for battery-powered warfighter applications. This is particularly important in EW applications, where the ability to operate for extended periods on battery power is a critical differentiator.

Figure 6 Chestnut SDR and FPGA solution.

Figure 5 shows a representative functional block diagram for the receive chain of an EW system. Figure 6 shows the Per Vices Chestnut SDR that can also be used in EW, radar or military communications applications. The Chestnut SDR offers four receive and four transmit radio chains that may each be independently controlled. Each chain of the platform has up to 500 MHz of bandwidth. The architecture allows for either a common LO or separately tuned LOs to be used to improve the coherency and stability for the applications requiring this architecture. The tuning range of Chestnut is from near DC to 9 GHz with 16-bit converters and dual 100GBASE-R digital throughput for up to 200 Gbps of data transfer. While the DC to 18 GHz frequency coverage of the Cyan SDR may be better suited to the most demanding EW applications, the Chestnut platform addresses applications, like EW, with fewer transceiver channels. The benefits of SDR, coupled with FPGAs turn the advantages described into real differentiators.

Benefits of FPGAs in SDRs for Military Communications

FPGAs offer several benefits for military communication systems when integrated into SDRs. Similar to the other applications discussed, one of the primary benefits is the ability of FPGAs to handle high speed data processing. Military communication systems require high data throughput rates to transmit and receive large amounts of data in real-time and FPGAs are capable of easily handling the required levels of data processing. FPGAs can be used to implement advanced digital signal processing algorithms, such as error correction and encryption, which are essential for ensuring the reliability and security of the communication system.

In military communications applications, SDRs with FPGAs utilize their ability to perform real-time signal processing to implement real-time filtering, modulation and demodulation. These capabilities are essential for improving the quality of the transmitted signal and reducing interference. FPGAs can also be used to implement adaptive filtering algorithms, which can automatically adjust the filter parameters based on the incoming signal.

In addition to these benefits, FPGAs can also be used to implement advanced modulation and demodulation schemes that are required in military communication systems. For example, FPGAs can be used to implement frequency-hopping techniques that are used to reduce interference and improve the reliability of the communication system. FPGAs can also be used to implement spread-spectrum techniques that are used to increase the security of the system. FPGAs also enable channelization in SDRs. This allows for the simultaneous processing of multiple channels. Channelizing becomes particularly useful in MilCom systems, where the ability to handle multiple channels simultaneously is essential for effective communication. The low latency signal processing in FPGAs is an essential differentiator in MilCom systems. Low latency in the signal chain means less time delay and this enables troops to communicate and make critical decisions faster and more efficiently, improving overall battlefield situational awareness.

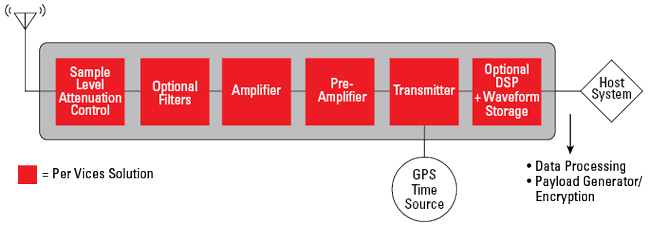

Figure 7 Representative EW system transmitter block diagram showing the Per Vices solution.

Figure 8 Crimson TNG SDR and FPGA solution.

Figure 7 shows a representative functional block diagram for a transmitter chain for a wireless receiver, whether that is for an EW system or a communications terminal. Figure 8 shows the Per Vices Crimson TNG SDR platform that can also provide value in radar and EW applications, in addition to communications applications. The Crimson TNG platform offers a radio architecture with four receive and four transmit chains. Each radio chain can be controlled independently, or it may share a common LO for better phase coherency and stability performance. Each radio chain has 325 MHz of bandwidth with 16-bit converters and a tuning range from near DC to 6 GHz. The digital interface for controlling the system is a standard 1G Ethernet port and the data transfer is done over dual 10GBASE-R interfaces, providing users with up to 20 Gbps of data transfer.

Summary

In conclusion, incorporating FPGAs into SDRs offer several benefits for radar, EW and military communication applications. The flexibility offered while accommodating real-time signal processing at high data rates allows this architecture to offer differentiated benefits and high performance in these applications. The additional benefits of low latency, reduced power consumption, the ability to modulate and demodulate data and being able to trigger the FPGAs externally increase the utility of these systems. For EW applications, these FPGA-based SDRs increase the ability of systems to detect, identify and counteract threats in the electromagnetic spectrum. In radar systems, the FPGA/SDR architecture improves system-level performance and accuracy, while simplifying the overall system complexity. In military communications applications, FPGAs coupled with an SDR can increase the performance and security of these systems.