By integrating commercially developed processing and high speed digitization at chip scale, new microelectronic devices are advancing the capabilities of defense systems.

The 21st century electronic battlefield is rapidly evolving, this is especially true for systems operating within the RF spectrum. We face adversaries using stealthy techniques and deploying advanced weapons. Countering those techniques and weapons requires extremely low latency responses from intelligent, adaptive applications. Practically, that requires a “quantum leap” in RF processing at the tactical edge.

While an injection of new technology is needed, it is not sufficient. Long-term success requires a continual process moving innovation from commercial electronics into defense systems. Sustained success also requires the technology innovations delivered to defense programs come from trusted and secure sources. Security threats from semiconductor tampering are like those from software breaches and are more difficult to detect.

Fortunately, a dynamic answer to the RF edge processing challenge comes from an adaptation of system-in-package (SiP) technology: the RFSiP. An RFSiP combines multifunction processing with the latest analog-to-digital and digital-to-analog converter (ADC/DAC) capability. Establishing technology partnerships among industry leaders, a high performance mixed-signal SiP is feasible at one-fifth the size of a small, printed circuit board (PCB).

NEXT-GEN RADAR AND EW

Electronic warfare (EW) systems are moving to ever-higher levels of complexity. Radars now use pulse widths lasting only nanoseconds. In addition to single frequency bursts, frequency hopping signals are across the RF spectrum. Other radar countermeasures include dynamically changing waveforms and patterns. To reliably detect these stealthy signals, EW systems must use higher sampling rates to continuously monitor the expanding bandwidths and frequency spectrum. 5 GSPS is no longer considered a high sampling rate; the bar is 50 GSPS.

For the EW system, detection is just the first step. It must be followed by effective responses created with low latency. This capability requires real-time processing for signal analysis and countermeasure generation, tightly coupled with the ADCs and DACs. The new generation of applications requires high data conversion rates with powerful processing to keep up with incoming signals.

One illustrative example is radar spoofing, where the EW system detects, alters and replays the radar’s pulses to create false and deceptively moving targets. This only works when the response latency is low, so the emitter radar does not perceive a time lag in the return pulse. In addition to maximizing rapid pulse detection and response, EW effectiveness depends on generating high spectral density across multiple channels, making high fidelity as critical as low latency.

Active radars have similar requirements. For example, a multifunction active electronically scanned array puts tremendous demands on embedded processing, as the radar must dynamically shift from surveillance of long-range threats to tracking and jamming short-range targets. The mode flexibility required can only be achieved when all available data is processed in real time.

New application areas add additional processing requirements. Cognitive radar applies artificial intelligence (AI) techniques to extract information about a target from a received signal, then uses the information to improve transmit frequency, waveform shape and pulse repetition frequency. Similarly, cognitive EW applies AI to identify patterns in the detected data to develop effective responses. Both cognitive radar and cognitive EW must execute their AI algorithms in near real-time. To do so, graphics processing units (GPUs) are added to RF processing, complementing the FPGAs that perform signal analysis and creation. Using many core processors is not the answer. While they can execute billions of instructions per second, they are not designed for low power consumption. They also need mixed-signal ICs and FPGAs for the RF interfaces, so a complete system requires a PCB.

Until recently, these multiple processing methods required distinct semiconductors, often assembled in a multi-board system. For RF applications, moving data from the ADC and DAC to centralized computing challenges data fidelity and latency. The current generation of converters are generating data bandwidths that overwhelm system interconnects, with transmission times that don’t support low latency radar and EW responses. This forces substantial data reduction before the central processor. To overcome these limitations, system architectures must move away from a centralized computing model to processing where the data is—at the tactical edge. Fortunately, new packaging technology helps solve that challenge.

INTEGRATION AND SWaP

RF edge processing requires multiple, tightly integrated functions working together to capture, analyze and manipulate a data stream in real time. Latency requirements favor ADCs and DACs that implement direct digital conversion. Efficient processing of the digital bit stream requires pipelined operations by some combination of FPGAs, GPUs and general-purpose processors. The components must connect via high bandwidth interconnects with low latency and be supplied with the required power. Everything must be assembled within a package small enough to be near the antenna.

The technology solution for RF edge processing comes from the commercial electronics market, which continually drives process and packaging technology with hundreds of billions of dollars in R&D investments every year. The mantra of commercial electronics is increasing functionality while miniaturizing, reducing power consumption and costing less. The much smaller defense industry can capitalize on the commercial investment by adopting and adapting new technologies to the unique requirements of defense applications. By leveraging commercial technology, the defense electronics industry can convert the basic research and invention cycle to adopting, adapting and maintaining the technology advantage over adversaries.

The commercial microelectronics industry is adopting heterogeneous integration (HI) of SiP technology. This capability assembles small semiconductor functions, called chiplets, on a small piece of Si. Each chiplet performs a specific function, such as the RF front-end, data conversion, digital signal processing, digital I/O or the dozens of functions in a mixed-signal data flow. Every chiplet is an individual semiconductor—even as complex as multicore processors. The chiplets can be combined and connected in many ways, each combination has a high performance subsystem or system optimized for an application. HI enables the multifunction, pipelined dataflow to be packaged into a SiP, much smaller than a PCB.

HI SiP FOR RF EDGE PROCESSING

A SiP created by Mercury Systems for RF sensor data processing will illustrate the concept and capability. The RFS1140 is one of a family of RFSiPs reflecting the practice of adopting technology from the commercial world and tailoring it for defense systems.

Processing Chiplet

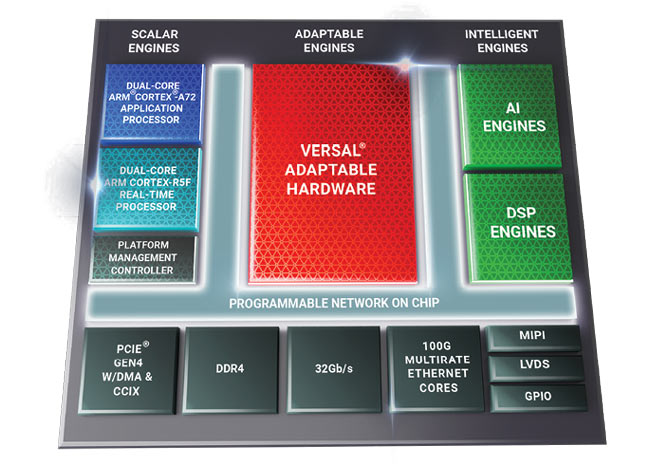

The RFSiP’s processing chiplet is a new semiconductor architecture, an adaptive compute acceleration platform (ACAP). The Versal® AI Edge ACAP from AMD-Xilinx is a heterogeneous processor, fabricated with 7 nm technology and incorporating three compute engines, much more than an FPGA or MPSoC. Each ACAP includes scalar processors, programmable logic and vector processors, all connected by a high bandwidth network-on-chip (see Figure 1).

Figure 1 AMD-Xilinx Versal AI Edge ACAP functional block diagram.

Multiple compute engine types are designed into the ACAP because no single style of processing can optimally perform all the tasks involved in a sophisticated edge application. Scalar processors, functioning like traditional CPUs, are ideal for complex decision-making and control. The AI Edge ACAP has four of these: two low-power ARM® Cortex®-R5F real-time processors and two full-power domain Cortex-A72 cores, supported by a system memory management unit. Programmable logic, also referred to as adaptable engines, adds flexibility to handle diverse and computationally demanding algorithms. Included are FPGA structures, with 1.5x the lookup tables (LUTs) of a Virtex chip, as well as programmable I/O and a customizable memory hierarchy of block RAM and UltraRAM. Vector processors, called intelligent engines, are optimized for advanced signal processing such as linear algebra and matrix math, which are well suited for 5G wireless systems and AI inference. The chip contains two types: DSP engines, which function like traditional digital signal processors, and AI engines, like advanced GPUs, which comprise vector processors for fixed and floating-point operations, a scalar processor and dedicated program and data memories. A single Versal ACAP chip provides 400 AI engines, 1968 DSP engines and more than 900,000 FPGA LUTs.

Data Converters

The processing in the RFSiP is combined with the extremely fast ADCs and DACs of the Electra-MA from Jariet Technologies. Each RFSiP has two of these low-power transceivers, yielding four ADC receive channels and four DAC transmit channels. All operate to 64 GSPS and can directly digitize frequencies through 36 GHz and operate in the first Nyquist zone to 32 GHz.

Power Converter

A Ferric power converter is a die power regulator that supports high current density. Three of these are used within the RFSiP, taking a single supply voltage and generating all the voltages needed by the other components. This power management architecture simplifies the RFSiP’s integration into larger systems.

SiP Integration

The AMD-Xilinx, Jariet and Ferric chips and 4 GB of DDR4 memory are integrated on an organic substrate in a 50 x 50 mm2 area. A high bandwidth interconnection, including a dedicated bus, moves data between the Jariet data converters and the Versal ACAP. This advanced RF capability is delivered in a package optimized for SWaP-C. The individual die are attached using thermal compression bonding and assembled in Mercury Systems’ dedicated microelectronics facility in Phoenix (see Figure 2).

Figure 2 Mercury Systems’ custom microelectronics packaging center in Phoenix.

ENABLING RF EDGE APPLICATIONS

Equivalent to multiple PCBs in currently deployed systems, the RFS1140 is a single, small package SiP. It enables tactical edge processing in very constrained spaces and lowers overall system cost. With direct digitization at extremely high sampling rates, the RFSiP enables systems to detect and monitor stealthy signals. By eliminating the down-conversion to an intermediate frequency, direct digitization achieves extremely low latency, even at 64 GSPS data rates. The RFSiP supports the processing requirements for tracking potential targets, including those moving at hypersonic speeds, and generates low latency responses. The AMD-Xilinx Versal ACAP in the SiP has an extensive set of heterogeneous math processing engines with both the processing power and flexibility needed by AI-based cognitive radar and EW applications.

Through close collaboration with the technology teams at Mercury, AMD-Xilinx, Jariet and Ferric, the SiP concept was adopted and rapidly adapted for RF edge processing. The SiP design approach enables future generations of semiconductor technology created by commercial R&D to rapidly upgrade defense systems while maintaining the same physical form factor.

TRUSTED SOURCING ESSENTIAL

Advanced microelectronics can give our forces a technical advantage on the battlefield. A key element to maintain that advantage is ensuring the trust and security of the microelectronics supply chain. The risks of a compromised supply chain are clear. Semiconductor tampering is extremely difficult to detect and can include hidden “backdoors” and remotely operated “kill switches.” While many cybersecurity discussions focus on software threats, semiconductor vulnerabilities may pose greater risks to DOD programs.

Scalable manufacturing operations within the U.S. are essential to the rapid deployment of secure microelectronics for defense programs. Organizations committed to the delivery of trusted solutions start with investments in processes and manufacturing capacity, followed by DMEA accreditation. Employing standardized design architectures and interfaces reduce technical and schedule risks and the likelihood of cost overruns, as well as ensuring trust and security in the supply chain.