Software Architecture

For the heterogeneous architecture of the XCZU9EG, different types of software are required. Procedure control, device initialization and configuration and multi-channel consistency calculation are implemented in software run on PS, while the JESD204B driver, the generation of reference waves, DMA transmission and other necessary logic resides in PL. The software architecture is shown in Figure 6.

Figure 6 Software architecture.

Initialization and Calibration Software on PS

AD9528 and ADRV9009s are configured first. After all the JESD204B receivers set the SYNC signal, the AD9528 is triggered to generate SYSREF. When initialization of the transceivers is complete, a calibration procedure is executed. Reference signals are looped outside the transceivers while the looped signals are captured by PL and analyzed by PS. The transceiver is ready after the calibration procedure is completed. This procedure, executed by software in PS, is outlined in Figure 7.

Figure 7 Software procedure.

Logic Design in PL

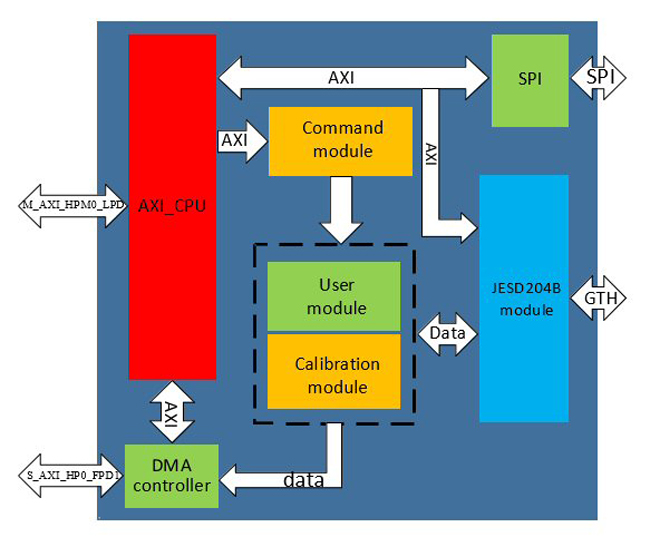

PL and PS are connected via the XCZU9EG AXI and HP buses in SPE. The logic design block diagram for PL is shown in Figure 8.

Figure 8 PL logic design block diagram.

PL and PS perform DMA data transmission via the S_AXI_HP0_FPD1 interface and perform command transmission through the M_AXI_HPM0_LPD interface. The AXI_CPU module sends commands to the JESD204B module, command module and the DMA controller for command analysis. The calibration control module generates DDS signals of predefined frequency and amplitude according to the configuration parameters of PS; and it sends DDS signals to the JESD204B module according to the calibration mode. The data collected is sent to PS for channel calibration through the DMA controller.

OPERATION

Transmitter Performance

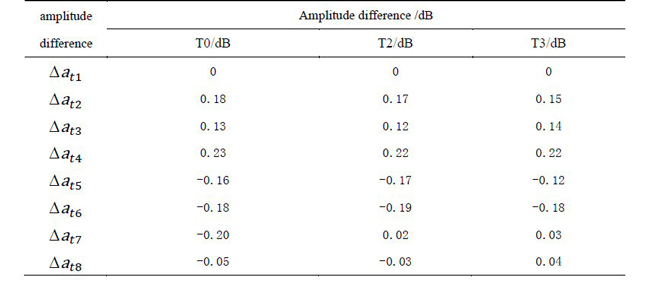

Multi-channel amplitude consistency of the transmitter is measured prior to calibration followed by the measurement of multi-channel phase consistency before and after calibration. The 16 transmit channels are connected to the calibration channel through a combiner. A 15.36 MHz sinusoidal signal is generated by PL and sent to the transmit channels with the calibration mode carrier frequency set to 2 GHz. PL collects the data and sends it to PS for calibration of transmit channels. The system is powered off and on again for multiple measurements. The first channel is used as a reference for calculating amplitude differences, where Δatn represents channel-to-channel amplitude differences between the nth ADRV9009 and the first ADRV9009 (see Table 1)

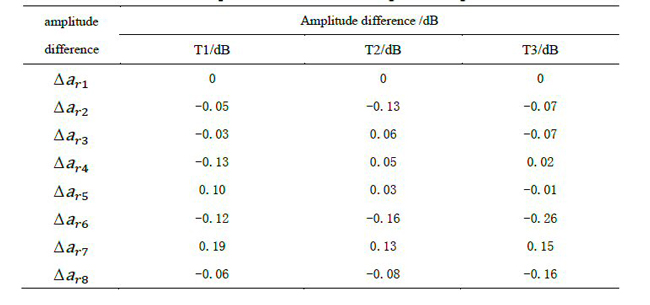

Table 1 Amplitude Differences Across Transmit Channels

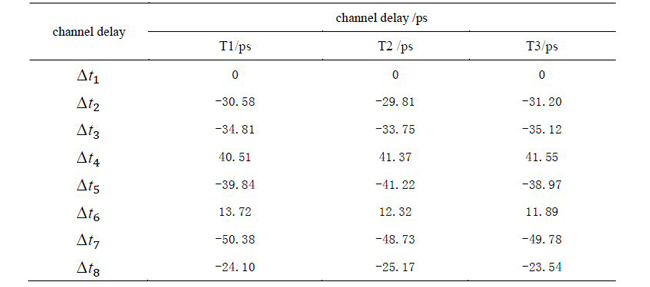

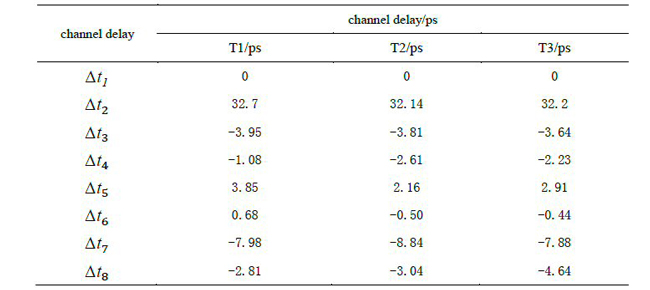

Table 1 shows that the transmit channels have good amplitude consistency, even without calibration. With the first channel used as a reference, the phase differences between the channels are calculated. The baseband signal phase differences are converted to RF signal channel delay errors according to tx=φx/(2πƒ0), where the carrier frequency ƒ0 is 2 GHz. The results are shown in Table 2, where Δtn represents the channel-to-channel delay error between the nth ADRV9009 and the first ADRV9009.

Table 2 Delay Differences Across Transmit Channels Before Calibration

After the calibration, the transmit channels are configured in the normal operating mode with the imported compensation data. The signals generated in PL are sent to the transmit channels again, and test results show delay errors among the transmit channels to be less than 4 ps.

Multi-Channel Receiver Performance

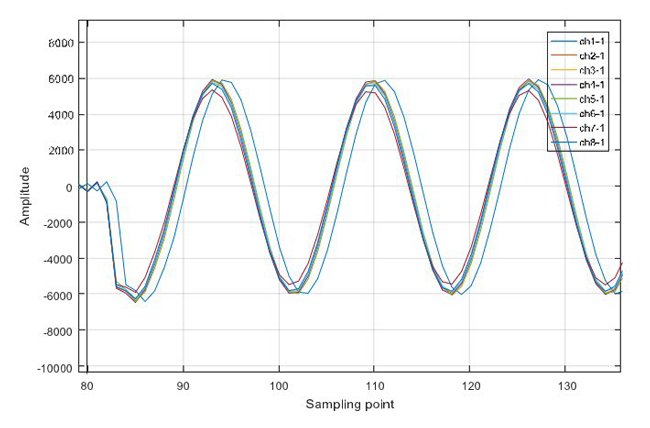

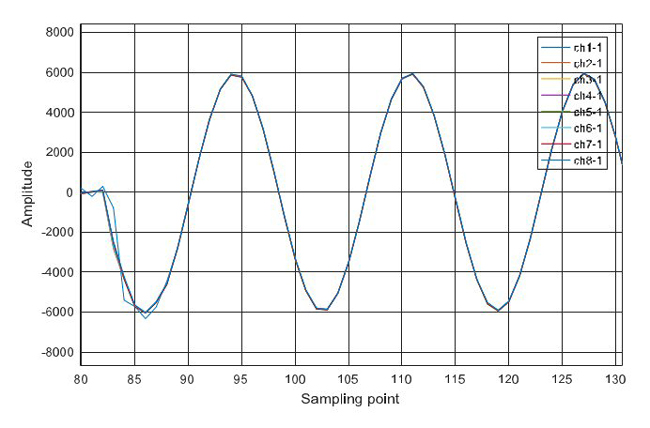

The receiver test process is like that of the transmit channels. A sinusoidal 15.36 MHz signal is generated in PL and sent to the calibration channel. The calibration channel is connected to the 16 receive channels through a splitter, and the data collected from the 16 channels is sent to PS for data processing. Waveforms of the raw data collected by eight of the channels is shown in Figure 9.

Figure 9 Received waveforms before calibration.

Based on the collected data, amplitude and phase differences are calculated. Using the equation tx=φx/(2πƒ0), phase differences are converted to time differences. The baseband signal amplitude differences of the receive channel are shown in Table 3. Delay errors between receive channels are shown in Table 4.

Table 3 Amplitude Differences Along Receive Channels

Table 4 Delay Differences Across Receive Channels Before Calibration

After the calibration procedure is complete, the receive channels are configured in the normal operating mode with the imported compensation data. The calibration reference signal is generated and captured again; then the captured data is exported and analyzed. Results show delay errors across the receive channels to be less than 1 ps (see Figure 10).

Figure 10 Received waveforms after calibration.

CONCLUSIONS

An SDR-based wideband MIMO transceiver was demonstrated with nine ADRV9009s and one heterogeneous Zynq UltraScale+ MPSoC XCZU9EG. The prototype implements both a 16-channel transmitter and a 16-channel receiver. It features good multi-channel amplitude-phase consistency, low power consumption, RF frequency agility and a 200 MHz maximum bandwidth.

References

- M. Wang, F. Gao, S. Jin and H. Lin, “An Overview of Enhanced Massive MIMO with Array Signal Processing Techniques,” IEEE Journal of Selected Topics in Signal Processing, Vol. 13, No. 11, August 2019, pp.886-901.

- A. Lestari, D. D. Patriadi, I. H. Putri and B.Harnaw, “FPGA-Based SDR Implementation for FMCW Maritime Surveillance Radar,” 2017 International Conference on Radar, Antenna, Microwave, Electronics and Telecommunication, October 2017.

- L. Xu, P. An, Y. Wang and J. Li, “Low Power Gated-Clock Design for Multi-Core DSP Based SDR Platform,” Science and Technology, Vol. 9, NO. 6, June 2016, pp.169-178.

- F. M. Ghannouchi,” Software-Defined Radio Transmitters for Advanced Wireless and Satellite Communications Systems,” Microwave Journal, Vol. 51, No. 5, May 2008.

- F. Tian, H. Li and L. Yuan, “Design and implementation of AD9361-Based Software Radio Receiver,” EURASIP Journal on Wireless Communications and Networking, Vol. 2019, No.1, December 2019.

- T. Shi, W. Guo, L. Yang and A. Li, “Remote Wideband Data Acquiring System Based on ZC706 and AD9361,” IEEE International Wireless Symposium, April 2015.

- W. Xusong, C. Shailesh, L. Mihir and C. Danijela, “Wideband Spectrum Sensing Measurement Results Using Tunable Front-End and FPGA Implementation,” Conference Record of 51st Asilomar Conference on Signals, October 2017, pp 499-503.

- M. Xie, S. Liu, D. Zhai and J.Yuan, “Application of Synchronous Acquisition Technology Based on JESD204B Protocol in Phased Array Radar,” 11th International Congress on Image and Signal Processing, October 2018.

- J. Yuan, M. Xie, S. Liu and D. Zhai, “Design of JESD204B Multi-Channel Data Acquisition and Playback System Based on SoPC,” 11th International Congress on Image and Signal Processing, October 2018.

- Z. Wu, C. Zhang, F. Li and Z. Wang, “High Speed Serial Interface Transceiver Controller Based on JESD204B,”14th IEEE International New Circuits and Systems Conference, June 2016.

- Y. Jiadong, X. Min, L. Siyuan and Z. Dengyue, “Design of JESD204B Multi-Channel Data Acquisition and Playback System Based on SoPC,” 11th International Congress on Image and Signal Processing, October 2018.