Technical Feature

Low Phase Noise SiGe Voltage-controlled Oscillators for Wireless Applications

A low phase noise voltage-controlled oscillator (VCO) is one of the critical circuits in modern telecommunications systems. In recent years, silicon germanium (SiGe) BiCMOS technology has become one of the most promising technologies for VCO designs. This article describes both transmit (Tx) and receive (Rx) VCO design solutions developed in high performance SiGe technology. The advantages of using SiGe BiCMOS technology for integrated VCO designs are addressed in detail. Examples of a Tx VCO using an off-chip tank and a fully integrated Rx VCO for GSM wireless handset applications are reported with design approaches and testing results.

Xudong Wang, Dawn Wang, Chris Masse and Peter Bacon

IBM Microelectronics

Lowell, MA

The VCO is a critical component of phase-locked-loop (PLL) frequency synthesizers. Phase noise is the most crucial performance parameter for VCOs since the phase noise of the frequency synthesizer is mainly determined by the contribution of the VCO, especially outside the loop bandwidth of the PLL. Besides the phase noise, strict requirements are placed on power consumption, VCO gain and other specifications including power supply pushing, load pulling, spurious response and harmonic levels, all of which need to be met in the targeted telecommunications system. Until now, module VCOs have often been chosen for use in cellular handsets because of the stringent phase noise and power requirements. As the wireless industry moves into the era of single-chip tranceiver systems, there is an increasing need to integrate the VCO function together with the rest of the synthesizer and tranceiver circuitries in order to reduce overall size and cost.

SiGe BiCMOS is considered one of the most promising and competitive technologies for the system-on-a-chip design of telecommunications ICs. It combines transistor performance competitive with III-V technologies and the advantages of low cost, process maturity and high integration levels common to silicon CMOS technology.

This article describes how SiGe BiCMOS technology can benefit integrated VCO design and how the SiGe BiCMOS process is used to develop a family of VCO ICs that meet requirements for GSM, CDMA, WCDMA and wireless LAN applications.

Using the GSM application as an example, the Tx VCO is required to have -165 dBc/Hz phase noise at 20 MHz offset frequency with a carrier frequency of 900 MHz. A core VCO solution is introduced that includes biasing and control circuitry, and the active devices for the VCO and buffer amplifiers. Only a discrete tank resonator and a few impedance matching components are off-chip for the GSM Tx VCO application. For the Rx VCO, a wide band, fully integrated VCO solution is provided to cover multiple wireless standards using a single VCO. Both of these solutions can lead to a single-chip integrated transceiver with only limited off-chip components for the Tx VCO.

SiGe BiCMOS Technology

SiGe BiCMOS technology has been widely used in telecommunications integrated chip (IC) designs because of its superior performance compared with the silicon BiCMOS and GaAs technologies.1 With the same CMOS performance, the SiGe heterojunction bipolar transistor (HBT) is the differentiation between SiGe BiCMOS technology and conventional silicon BiCMOS technology. Using bandgap engineering with optimized Ge profiling, SiGe HBTs can satisfy the product requirements for simultaneous high cut-off frequency ft , low base resistance, high Early voltage and high breakdown voltage, which cannot be achieved by silicon homojunction devices. A SiGe HBT with a cut-off frequency of 210 GHz has recently been reported. The fabrication processes for SiGe devices are compatible with those routinely used for Si ICs, which is a major advantage for Si/SiGe over GaAs technology. This compatibility ensures the continued use of existing Si IC foundries for manufacturing ICs on large size silicon wafers, which makes SiGe more cost-effective than GaAs for technological evolution. By using SiGe BiCMOS technology, RF front-end, baseband and digital signal processing circuitries for telecommunications systems can be readily integrated together on the same chip.

SiGe BiCMOS technology offers many benefits for integrated VCO design, especially concerning phase noise performance. Both the phase noise floor and close-in phase noise can benefit from using the SiGe BiCMOS HBT. The main contributors to the phase noise floor of a VCO are the shot noise of the active devices, thermal noise from the passive and active devices connected with the tank, and noise injected from the biasing circuitry. The SiGe HBT offers high cut-off frequency while achieving low noise figures and is well suited for low phase noise VCO designs. The minimum noise figure of the active device is the dominant factor in establishing the noise floor level of the VCO. The close-in phase noise is decided mainly by the loaded Q of the VCO tank circuit, the flicker noise and the corner frequency of the VCO active device. SiGe HBTs have low flicker noise and very low corner frequency that help make them very attractive for achieving low phase noise in the close-in offset frequency region.

|

Table 1 | |||

|

Parameter |

5HP |

6HP |

7HP |

|

AE (mm2 ) |

0.5 x 2.5 |

0.44 x 3 |

0.18 x 0.82 |

|

b |

100 |

100 |

200 |

|

VA (V) |

65 |

75 |

120 |

|

BVCEO (V) |

3.35 |

3.35 |

2.50 |

|

BVCBO (V) |

10.5 |

10.5 |

7.5 |

|

Rb@100mA (W) |

124 |

114 |

60 |

|

ft (GHz) |

47 |

47 |

90 |

|

fmax (GHz) |

65 |

65 |

90 |

|

NFmin (dB) |

0.8 |

0.8 |

0.4 |

Three generations of SiGe BiCMOS technology1 are offered: SiGe 5HP/AM (0.5 mm), SiGe 6HP(0.25 mm) and SiGe 7HP (0.18 mm). A comparison of the HBT (NPN) characteristics of these three generations are summarized in Table 1 . Besides NPNs, a full suite of high performance active and passive devices is available in each technology generation. For example, NPN, high breakdown NPN (NPNHB), gated lateral PNP (GLPNP), NMOS, PMOS and different types of resistors, capacitors, diodes and inductors with scalable models are available in the SiGe5HP/ AM technology. Table 2 summarizes the devices that are offered in SiGe5HP/AM process.1-3 The design kits support the platforms of both the Agilent Advanced Design System (ADS) and the Cadence Spectre giving the design engineer more freedom in choosing a design tool.

|

Table 2 | ||

|

Device Category |

Device |

Figure of Merit |

|

NPN SiGe HBTs |

Standard High breakdown |

ft =47 GHz |

|

FETs |

NFETs |

gm,sat =195 mS/mm |

|

LPNPN |

Gated LPNP |

gm /Ic=7.9 mS/mA |

|

Diodes |

Schottky |

Vf =0.31 V |

|

Capacitors |

MIM |

C=0.7 mm2 |

|

Inductors |

Thick last metal |

L=1.0 nH, |

|

Resistors |

Poly Si |

Rs=220 W/sq |

In addition to the superior HBT performance from SiGe BiCMOS technology, this specific process provides other advantages to the integrated VCO design. First, a higher voltage swing can be applied to the VCO with the high breakdown NPNs. To achieve low phase noise, the output voltage swing is designed to be as large as possible. Yet the breakdown voltage of a standard NPN restricts the peak VCO voltage swing. The high breakdown NPN with a BVCEO of 5.5 V can permit a large voltage swing at the VCO output. At low current density levels, the high breakdown device has the same level of low noise performance as the high ft devices. For the VCO, the active device is typically biased at low current density levels to achieve a low noise figure and thereby a low phase noise floor. Thus, the high breakdown device does not introduce extra noise compared with the case of using the high ft device but does provide the benefit of allowing a larger voltage swing for better phase noise performance. Second, better substrate isolation can be achieved by applying the deep trench isolation structure. In SiGe BiCMOS technology, a 6 mm deep trench isolation structure can be used under passive devices and around active devices or circuit blocks. When the deep trench is applied under passive devices such as resistors, metal-insulator-metal (MIM) capacitors and spiral inductors, the parasitic capacitances from these passive devices to the substrate is reduced. Finally, high Q inductors can be realized by the thick last level metal. For passive devices, the quality factor (Q) of the tank inductor has been the roadblock hindering VCOs from being fully integrated on silicon. Inductors built on silicon substrates from most technologies can only achieve unloaded Q values of less than 10 in the 1 GHz frequency range. In SiGe technology, analog metal (AM) is offered to make the high Q inductor design possible. The AM metal is made of thick aluminum alloy, offered in two production processes (5HP 0.5 mm technology and 6HP 0.25 mm technology). Besides the AM metal, the deep trench isolation discussed earlier can be used to reduce the substrate loss to further improve the inductor Q. Another option is to use a patterned poly-silicon ground plane underneath the inductor to provide shielding to minimize the magnetic loss of the inductors. With all of these technology attributes, a Q of 17 can be achieved for a 1 nH inductor at 5 GHz by using a standard inductor device from the device library. Custom designed inductors, such as differential inductors, can be optimized for the maximum Q at a specified operating frequency. Differential inductors have higher Q when used in a differential VCO topology due to the partial cancellation of the substrate effects.4 A differential inductor with an unloaded Q value as high as 27 at 4 GHz has been achieved.

Core VCO

The core VCO solution is provided for applications where very low phase noise, which cannot be presently accomplished by fully integrated solutions, is required by the telecommunications system. Using an off-chip tank and a few impedance matching components, the core VCO provides a good compromise between a module VCO and a fully integrated VCO while delivering ultra low phase noise. Not only can the core VCO be integrated into a full transceiver IC, but it can also be a low cost, competitive solution used by module manufactures to build stand alone VCOs.

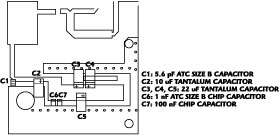

Fig. 1 Functional diagram of the core VCO.

A multi-mode core VCO has been successfully manufactured using 5HP/AM technology. With most of the VCO circuitry on-chip, such as HBT devices, the biasing and control circuit as well as the output buffer amplifier, three output signals with different output power can be generated from the two VCOs. The VCO's block diagram is shown in Figure 1 . Using a low temperature C4 die bumping technology, the IC die area is reduced to 1.13 mm by 2.25 mm and the package parasitic inductance is minimized. With the resonant tank components off-chip, this IC provides design flexibility over a fully integrated VCO in that the VCO frequency can be easily adjusted to other applications.

An evaluation board was designed to demonstrate the performance of the core VCO IC in a tri-band GSM Tx application. This board has been designed to provide up to +7 dBm at the high power outputs and -4 dBm at the prescaler output. Figure 2 shows the schematic of a tri-band GSM Tx VCO. Using standard inexpensive inductors, a phase noise of -165 dBc/Hz for the GSM900 Tx band and -158 dBc/Hz for the GSM1800 Tx band at 20 MHz offset from the carrier have been demonstrated.

Fig. 2 Schematic of a tri-band GSM transmitter VCO.

Fully Integrated VCO

A fully integrated VCO is necessary for true system-on-a-chip realization of wireless transceivers. Several design challenges must be overcome for the VCOs to be fully integrated on a silicon substrate. Meeting stringent phase noise requirements is one of the most difficult issues to be solved for the VCO design because high Q inductors and varactors are very difficult to realize on lossy silicon substrates. The bandwidth of the VCO is another important issue that needs to be addressed. With multiple standards co-existing in the wireless industry today, one single VCO covering the wide frequency range required by multiple standards is preferred for smaller chip area and easy system configuration. For example, in a triple band GSM application (GSM900/1800/1900), a single VCO operating at 3.8 GHz center frequency with a wide bandwidth can be used to cover the GSM1800 and GSM1900 application by dividing the VCO frequency by 2 and cover the GSM900 application by dividing the VCO frequency by 4. To make the VCO design even more challenging, the process variation of an on-chip device, especially the capacitance of the varactor and MIM capacitors, will further increase the required VCO frequency coverage to ensure that the bandwidth is met over all process variations. The supply voltage specified in handset applications is typically less than 3 V. Thus, it is very difficult for an integrated VCO with a single varactor as the sole tuning device to cover the required bandwidth of a cellular phone operating in multiple modes, such as in the triple band GSM application. With a larger bandwidth requirement, the VCO phase noise performance is even more difficult to meet. Even if a wide band VCO can be realized with a single varactor, the combination of a wide tuning range and low tuning voltage range (decided by the low power supply voltage) will result in a very high VCO gain. The higher VCO gain makes the oscillator much more sensitive to supply noise and spurious signals from the analog Vtune line.

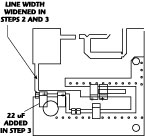

Fig. 3 VCO schematic.

To design a fully integrated VCO with a large bandwidth and a smaller VCO gain, an innovative topology is designed.5 By splitting the whole frequency range into multiple sub-bands, the analog tuning range is reduced dramatically. The VCO frequency tuning will be the combination of digital band switching for coarse frequency tuning and analog voltage tuning for fine frequency tuning. As a result, wide band VCOs for multi-mode wireless communications can be achieved. The fully integrated VCOs reported are designed using a cross-coupled differential configuration shown in Figure 3 .5-7 The cross-coupled capacitors provide the positive feedback to transistors Q1 and Q2 for the oscillation to start. The resistive degeneration of R1 helps reduce the common mode gain of the NPNs thereby reducing common mode signals such as the low frequency noise injected from the biasing circuitry. The varactors D1 and D2 are connected directly to the power supply (Vcc ) with minimum layout interconnect loss so that good phase noise can be achieved. In this configuration, the VCO will have a negative VCO gain slope.

In the tank circuit, total capacitance is the addition of the capacitances from a group of MOSFETs (N1 to N8) and varactors (D1 and D2). The drain and source terminals of the MOSFETs are shorted and the MOSFETS are used as digital varactors. The MOSFETs are binary sized to get 16 bands with four control lines. The voltages applied to the control lines are switched digitally between Vcc and ground, so the MOSFETs are only used in their ON and OFF states. Because there is no current flowing between the drain and source, there is no flicker noise generated by these MOSFETs. The Qs of the MOSFETs, in their ON and OFF states, are as high as 80 at 3 GHz, which is greater than that of the on-chip varactor. Therefore, the overall Q of the total tank capacitance is improved compared to a single larger varactor with an equivalent capacitance. In this VCO, the digitally controlled MOSFETs provide coarse tuning of the output frequency and the varactors, controlled by an analog Vtune voltage, will provide the fine frequency analog tuning required to function in PLLs. MOSFETs have a capacitance tuning ratio of 2-to-1 when switched between states, as shown in Figure 4 , but the varactor has a tuning ratio of 1.5-to-1 for the typical tuning voltage range of 0.4 to 2.4 V. As a result, the VCO's frequency tuning range is expanded when digital coarse frequency tuning and analog fine-tuning are combined.

Fig. 4 MOSFET capacitance behavior as a varactor.

The configuration shown in the VCO schematic provides additional advantages besides a large frequency tuning range. Because the MOSFETS are operating in the ON and OFF states, and their capacitances are much less sensitive to the supply voltage change, the VCO frequency is less sensitive to the supply voltage change compared with the case of using a large varactor as the only frequency tuning component. Therefore, the VCO topology has more immunity to supply noise and supply push. Another advantage of using capacitance from both the MOSFET and varactor in the tank is that the frequency sensitivity to temperature is improved due to the fact that the MOSFET capacitance is less sensitive to temperature than that of the varactor.

By using the combined digital tuning and analog frequency tuning, the VCO gain will be smaller, which favors the system-on-a-chip integration. With a smaller VCO gain, the VCO phase noise is less sensitive to the noise and jitters injected or coupled from other circuitries integrated on the same chip. On the other hand, the smaller VCO gain will be able to sustain relatively larger thermal noise voltages generated by the resistors of the loop filter on the analog tuning line compared with a VCO with a large VCO gain. As a result, it is easier to integrate a low pass loop filter on-chip because a smaller capacitor and a larger resistor (ensuring the same RC constant) can be used in the loop filter design to achieve the same loop bandwidth.

The disadvantage of applying the digital tuning scheme is that the VCO digital bands must be calibrated for process and temperature variation before it can be used in a frequency synthesizer system. Thanks to the large scale CMOS capability in the BiCMOS technology, the calibration scheme can be easily integrated either in conjunction with the synthesizer or in the VCO circuitry.6

With a given maximum power consumption, the phase noise performance of a VCO is mainly limited by the Q of the tank components including on-chip inductors, capacitors and varactors. The tank impedance selection will influence the tank Q, power consumption and phase noise performance directly. A higher capacitance value in the parallel resonator will result in better phase noise performance and larger frequency tuning range. However, for a given frequency, the higher the capacitance value is, the smaller the inductance will be. A smaller tank inductor will lead to lower load impedance to the transistors, thus a lower voltage swing for the same current consumption. On the other hand, a high Q inductor with a small inductance value is easier to achieve on-chip than one with a large inductance. With differential VCOs, differential inductors with a unloaded Q of greater than 27 at 4 GHz are realized using the thick AM top metal with deep trench substrate isolation. The inductor is modeled and simulated using Agilent Momentum.

Results

Results for three fully integrated VCOs for different applications with low phase noise are reported below. The chips are all fabricated using the 0.5 mm SiGe BiCMOS production process. This process includes four levels of metal with a thick analog metal layer. The varactors are made from the collector-base junctions of HBTs. A moat structure consisting of deep trench and grounded substrate rings are used for isolation between circuit blocks.

Fig. 5 Frequency coverage of a dual-band receiver VCO after divided by 4 for GSM900 band.

The first VCO is designed for dual-band GSM and DCS applications. Its core operates at a fundamental frequency of 3.6 GHz and frequency dividers are integrated with the VCO on the same IC. The VCO core frequency is divided by 4 and 2 for GSM and DCS applications, respectively. The output frequency at the DCS band is shown in Figure 5 . The VCO achieves a phase noise of -115 dBc/Hz in the DCS band at an offset frequency of 90 kHz.

The second universal, integrated VCO is designed to have a wide frequency tuning range of 3.4 to 4.6 GHz. This VCO can be operated over a considerable range of supply voltages between 2 to 3 V with only small deviations in RF performance. Applications for this VCO are targeted for wireless LAN and digital wireless handsets.

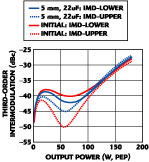

The third VCO operates at 3.3 to 4 GHz with a positive VCO gain. It demonstrates improved phase noise and supply push performances over the first VCO. Assembled in a QFN20 package, a phase noise of -143.2 dBc/Hz at 3 MHz offset frequency has been measured for a carrier frequency of 3.37 GHz, as shown in Figure 6 . The supply pushing is less than 2 MHz per 0.1 V supply change. The load pulling is less than 1 MHz for a 2:1 SWR load impedance change across all phases. The VCO has a cascoded differential buffer amplifier to provide 0 dBm output power to a 100 W load, which is commonly sufficient to drive mixers in the tri-band GSM receiver directly. The harmonic levels are as low as -30 dBc. Operated at a nominal 2.8 V supply, the VCO draws 15 mA total current, including 5 mA consumed by the output buffer.

Fig. 6 Phase noise performance of a VCO operating at a carrier frequency of 3.37 GHz.

Conclusion

SiGe technology has proven to be a top candidate for low phase noise integrated VCO designs. The core VCO, using a few off-chip components for the tank resonator and impedance matching, is used in a GSM Tx VCO application and its performance reviewed.

A single, fully integrated, wide band integrated VCO covering tri-band GSM receiver requirements is attractive for direct conversion receiver configurations. It is presently usurping off-chip tank solutions in the next generation production lines and enabling single-chip VCO/PLL synthesizer solutions. The performance of both the Tx VCO and the Rx VCO meet the demanding requirements of GSM applications and can be integrated into single-chip transceiver solutions.

Acknowledgment

The authors wish to acknowledge the assistance and support of William Vaillancourt, Matthew Allen, David Carr, Kurt Sckelkle, Jean-Marc Mourant and Jim Imborone.

References

1. D. Harame, D. Ahlgren, D. Coolbaugh, J. Dunn, G. Freeman, J. Gillis, R. Groves, G. Hendersen, R. Johnson, A. Joseph, S. Subbabba, A. Victor, K. Watson, C. Webster and P. Zampardi, "Current Status and Future Trends of SiGe BiCMOS Technology," IEEE Transactions on Electron Devices , Vol. 48, No. 11, November 2001, pp. 2575-2594.

2. D. Greenberg, "SiGe BiCMOS Technology for RF/Analog/Mixed-signal Applications," IEEE RFIC Symposium , WSA02B Workshop, June 2000.

3. J. Pusl, S. Sridharan, P. Antognetti, D. Helms, A. Nigam, J. Griffiths, K. Louie and M. Doherty, "SiGe Power Amplifier ICs with SWR Protection for Handset Applications," Microwave Journal , Vol. 44, No. 6, June 2001, pp. 100-113.

4. H. Ainspan and J.O. Plouchart, "A Comparison of MOS Varactors in Fully-integrated CMOS LC VCOs at 5 and 7 GHz," European Solid-State Circuits Conference , Stockholm, Sweden, September 19-21, 2000.

5. J.M. Mourant, J. Imbornone and T. Tewksbury, "A Low Phase Noise Monolithic VCO in SiGe BiCMOS," 2000 IEEE RFIC Symposium Digest, June 2000, pp. 65-68.

6. X. Wang, D. Wang, D. Chang, A. Eshraghi, P. Bacon, V. Pereira, P. Rivenburgh and K. Schelkle, "Fully Integrated Low Phase Noise VCO with Auto-calibration In SiGe BiCMOS Technology," Proceedings of European Conference on Wireless Technology , ECWT2001, London, England, September 2001, pp. 307-310.

7. X. Wang, D. Wang, K. Schelkle and P. Bacon, "Fully Integrated Low Phase Noise VCO Design in SiGe BiCMOS Technology," Proceedings of the 2001 IEEE Radio and Wireless Conference , Boston, MA August 2001, pp. 109-112.

Xudong Wang received his PhD degree from Northwestern Polytechnical University in 1995. Between 1995 and 1999, he was a postdoctoral research fellow working in the department of electrical engineering at the University of Utah. In 2000, he joined IBM Microelectronics as an RF design engineer. His activity includes RF and microwave IC design, EM analysis and nonlinear circuit design. Currently, he is focused on the design of RF front-end circuits for wireless communications.

Dawn Wang earned her BSEE and MSEE degrees from Tsinghua University, China, in 1985 and 1987, respectively, and her MS degree in solid state physics from Arizona State University in 1993. She was a device engineer at Burr-Brown Corp. (now Texas Instruments Inc.) from 1995 to 1998. She is currently a circuit designer developing various radio frequency integrated circuits for wireless communication handsets at IBM.

Chris Masse received his engineering degree from the Ecole Nationale Superieure d' Electronique et de ses Applications (E.N.S.E.A, Cergy Pontoise, France) in telecommunication and microwave engineering in 1997. He has worked on RF and microwave PLL design, and has recently been engaged in the development of VCOs on L.T.C.C. substrates with a special focus on the integration of discrete components inside the substrate. Joining the IBM Boston Design Center at the beginning of 2001, he has been involved in evaluation of the performance of SiGe circuits and design of low noise, low cost, multi-band VCOs.

Peter Bacon received his BSEE and MSEE degrees from Lehigh University in 1983 and 1985, respectively, and his MBA from Boston University in 1994. He started his engineering career in 1984 with Harris Microwave Semiconductor, designing broadband C-Band and Ku-band GaAs MMIC amplifiers and supporting foundry model and design kit development. In 1988, he joined Raytheon Co. focusing on commercial GaAs IC design and development for applications in the Ku-band DBS and VSAT satellite markets. In 1998, he joined IBM Microelectronics Division, where he is presently the Boston Design Center manager. The Boston Design Center emphasizes RF and analog IC development for wireless and digital handset applications utilizing IBM's SiGe BiCMOS technology.