Technical Feature

SOI CMOS Technology For RF System-on-chip Applications

CMOS technology is one of the most promising choices for RF applications. Its highly integrated nature provides true RF system-on-chip integration. Silicon-on- insulator (SOI) CMOS offers specific additional design advantages that include a significant reduction in cross-talk between RF and digital circuits on the same die and easy integration of high quality passive elements. Basic RF building blocks through 6 GHz have been verified with a 0.35 mm production-ready SOI CMOS technology.

Jerry Yue and Jeff Kriz

Honeywell Solid State Electronics Center

Plymouth, MN

Gallium arsenide (GaAs) has been used extensively for 2 to 6 GHz RF applications due to its intrinsically higher speed. Whenever cost and integration are important technology selection criteria, CMOS is an excellent choice. This is especially true with the advance in CMOS technology, where an ft beyond 140 GHz is readily demonstrated.1 Recently, a single chip, 2.4 GHz transceiver for Bluetooth application has been successfully demonstrated with a deep sub-micron CMOS technology,2 and 900 MHz Industrial, Scientific and Medical (ISM) band transceivers with a direct microcontroller interface have been fabricated.13 The recent announcement of a single chip, 5 GHz wireless local area network (WLAN) further illustrates the point that CMOS is a viable solution in complicated RF systems.3 The minimum noise figure, which is an important characteristic in RF front-end design, has also been improved with scaled CMOS. Noise figures as low as 0.2 dB have been reported with proper device layout.4

Low power consumption is particularly important in mobile communications due to limited battery life. One approach to meeting this challenge is to create a reduced power RF system-on-chip that contains digital, analog and RF portions of the design on the same die. SOI CMOS meets these requirements due to its reduced parasitic capacitance.5 The presence of the buried oxide layer not only reduces the junction capacitance but also offers the flexibility of using a high resistivity substrate to reduce the substrate-related RF loss. Microstrip losses as low as 0.03 dB/mm have been realized on high resistivity substrates at 2 GHz compared with 0.1 dB/mm on standard substrates.6 In addition, improved passive device performance (resistor, capacitor and inductor) over frequency has also been demonstrated on SOI substrates.

Another key concern with highly integrated RF/mixed mode circuit design is how to eliminate the cross-talk between high frequency RF and digital, mixed signal devices on the same die. This can be drastically reduced by using fully oxide-isolated SOI CMOS technology. Complete oxide isolation of the active devices from the substrate eliminates the substrate current injection path.7 In this article, a review of the current advances in RF SOI CMOS is provided.

|

Table 1 | |||

|

Category |

SEMATCH Estimation |

Revenue Gain vs. Bulk CMOS |

Latest Industry Benchmark |

|

Process steps |

20% less process steps |

Simpler well, isolation |

Between 10-20% simpler |

|

Mask counts |

3 less masking steps |

Simpler well, isolation |

Between 1-3 fewer masks |

|

Circuit density |

1.3x improvement |

Tighter isolation, latch up rules |

30% better |

|

Performance |

30% faster |

Lower capacitance *ASP=Average Selling Price |

Technology generation dependence |

SOI Technology

|

|

|

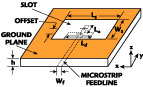

Fig. 1 Cross-section of a four layer metal SOI device. |

SOI substrates have been fabricated by either oxygen implant/anneal (SIMOX) or bond/etch back (BESOI) techniques. Both have gained acceptance in the market place. Anticipated wafer volume is in the range of 500,000 wafers per year ramping to 10 million per year by 2005. Recently, the two largest SIMOX and BESOI suppliers have formed an alliance with major commercial silicon wafer suppliers to further secure the needed wafer capacity. This milestone illustrates the general acceptance of SOI as a viable technology choice. Large volume production is the only way to ensure continuous price reduction and quality improvement. This is where SOI has a significant advantage over other insulated materials such as silicon-on-sapphire (SOS). Companies such as IBM, Honeywell, AMD, Motorola, Samsung, Matsushita, XFAB and many others are actively producing SOI-based integrated circuits.

Today, RF SOI CMOS-based products operate in the 2 to 10 GHz range without compromising RF performance. As early as 1994,8 SEMATECH completed an analysis of SOI and bulk CMOS technology that concluded that SOI has the potential to be a lower cost solution because the simpler well/isolation process requires fewer processing steps, thus lowering manufacturing cost. In addition, the study revealed, a higher die leverage, due to improved isolation, yields more good die per wafer and higher performance results from the elimination of substrate capacitances. Table 1 summarizes SEMATECH's original work with updates from some recent publications. Even though the comparison was done with digital SRAM in mind, its conclusion still applies to mixed mode technology.

|

|

|

Fig. 2 Typical performance comparison between bulk and SOI CMOS technology. |

A cross-section of a multi-layer metal SOI device is shown in Figure 1 . A silicon thickness ranging from 50 to 200 nm has been used to fabricate the transistors. With such a thin-film, source and drain junction/depletion width of the MOS transistors can be easily bottomed to the buried oxide, thus reducing the junction capacitance. Combined with the fact that power consumption is directly proportional to the capacitance (power » CV2 ), SOI technology is playing an increasingly important role in low power mobile application. A typical performance comparison between bulk and SOI technologies is shown in Figure 2 .9

Substrate Cross-talk Reduction

To integrate an RF system-on-chip, it is important to have proper device isolation in the gigahertz frequency range. SOI technology provides the proper device isolation because complete oxide isolation between devices essentially cuts off all direct paths of substrate injection noise and a near intrinsic substrate further reduces the capacitive coupling through the substrate. Complete oxide isolation is impossible to form with bulk CMOS or bipolar technology. To overcome this problem, multiple substrate contacts with large guard band and/or deep trench isolation to reduce the substrate injection current can be used. Either approach suffers a negative impact on density (large guard band) or higher fabrication cost (complex processing of deep trench isolation structures).

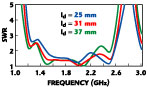

As pointed out earlier, the buried oxide layer offers a complete isolation between the active device region and the bulk substrate. This provides an additional degree of freedom in selecting the high resistivity substrate. Using a near intrinsic substrate to reduce the capacitive coupling is impossible for bulk technology due to latch up concerns. A pad-to-pad isolation measurement up to 10 GHz is shown in Figure 3 , where SOI shows a near 30 to 40 dB improvement.

|

|

|

|

Fig. 3 Pad-to-pad isolation comparison between bulk and SOI devices at 160 mm separation. |

Fig. 4 Inductor Q vs. frequency. |

Substrate Loss Reduction

Microstrip Loss Reduction

In addition to the above-mentioned cross-talk reduction, a high resistivity substrate further reduces the microstrip loss at high frequency. Since microstrip is widely used for impedance matching, it is important to address the substrate loss issue. Recent studies have shown that on a substrate with a resistivity of 1 kW-cm, the loss of a microstrip line at 2 GHz is only 0.03 dB/mm compared with 0.55 dBm/mm on a typical 50 W-cm substrate.5 A factor of 18 improvement is easily achievable on SOI substrate. This comparison is summarized in Table 2 .

|

Table 2 | ||

|

Substrate |

Resistivity |

Loss |

|

Semi-insulated |

106 |

0.03 |

|

Low resistivity |

50 |

0.54 |

|

High resistivity |

103 |

0.05 |

Inductor Loss Reduction

Figure 4 shows the estimated inductor Q vs. frequency for SOI technology. Substrate resistivity plays a key role in determining the inductor Q at high frequencies. Recently, a simple inductor model has been proposed where the roll-off of the Q value at high frequency is dominated by the substrate loss.10 This can easily be improved by using a high resistivity SOI substrate. A Q of approximately 10 at 5 GHz has been achieved with a simple two layer standard metal process instead of the costly five or six layer thick metal required by the advanced CMOS processes. This is an important attribute of the SOI technology, since not all the RF system-on-chip requires a five or six layer metal interconnect process. One side benefit, of course, is the reduction of the cycle time to manufacture the products.

Resistor/Capacitor Loss Reduction

|

|

|

Fig. 5 Substrate-related RF loss showing a significant reduction in the 400 W polysilicon resistor example. |

An improvement in resistor performance is also observed on SOI. Comparing a 400 W polysilicon resistor, SOI behaves close to the ideal resistor through 18 GHz; bulk resistor, however, suffers from substrate coupling and degrades at frequencies as low as 5 GHz, as shown in Figure 5 . A similar improvement in capacitor performance is also observed at high frequencies. Since passive elements such as inductors, resistors and capacitors all play a very important role in RF front-end design, high resistivity SOI offers an obvious performance advantage over bulk technology.

Noise Figure/PAE Improvement

Gate-degenerated topology is widely used for low noise amplifier (LNA) designs in RF applications. The input inductor, which is directly connected to the gate, could introduce a substantially large amount of capacitive coupling to the substrate, thus degrading both ft and noise figure (NF) directly. At least 0.5 dB NF improvement over bulk CMOS has been reported at 2.5 GHz by using the SOI process with a high resistivity substrate.11

Input inductor coupling could also cause degradation in LDMOS performance as explained by Fiorenza.12

SOI CMOS Integration Capability

Since SOI CMOS is a silicon-based technology, a high level of integration can be obtained. An example is shown in Figure 6 , where a six-bit digital attenuator is integrated with a sophisticated control logic. With early 0.8 mm RF SOI technology, this product has demonstrated good performance characteristics from 300 MHz to more than 1 GHz and is usable to 2 GHz. A variable gain amplifier with 22 dB of gain and 60 dB attenuation in 0.5 dB steps has also been realized with SOI CMOS technology. This frequency range can easily be extended to 4 GHz with a 0.35 mm SOI CMOS technology.

|

|

|

Fig. 6 An example of a highly integrated six-bit attenuator. |

Conclusion

SOI CMOS is a cost-effective, viable technology for RF system-on-chip integration up to 10 GHz due to its ability to achieve higher levels of device integration without compromising RF performance. Reduction in cross-talk and easy integration of passive elements are key attributes to SOI CMOS technology.

Acknowledgment

The authors wish to acknowledge the assistance and support of David Wick in reviewing this paper, and the Allied Signal/Honeywell International Microelectronic Technology Center (MTC) for developing the advanced RF SOI CMOS technology.

References

1. Y. Momiyama, et al., "A 140 GHz Ft and 60 GHz Fmax DTMOS Integrated with High Performance SOI Logic Technology," 2000 IEEE Electron Device Meeting (IEDM) , December 2000, p. 455.

2. H. Darabi, et al., "A 2.4 GHz CMOS Transceiver for Bluetooth," 2001 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium , May 2001, pp. 89-92.

3. T.H. Meng, et al., "Wireless LNA Revolution: From Silicon to Systems," 2001 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium , May 2001, pp. 3-6.

4. T. Ohguro, et al., "RF Circuit Design on CMOS," 2000 IEEE MTT-S International Microwave Symposium , workshop notes "Integrated Transceiver Design Using Silicon Based Semiconductor," June 2000.

5. F. Assaderaghi, et al., "A 7.9/5.5 psec Room/Low Temperature SOI CMOS," 1997 IEEE Electron Device Meeting (IEDM) , December 1997, pp. 415-418.

6. N. Suematsu, et al., "On-chip Matching Techniques for Si-MMICs," 2000 IEEE MTT-S International Microwave Symposium , workshop notes "Integrated Transceiver Design Using Silicon-based Semiconductor," June 2000.

7. M. Kumar, et al., "A Simple, High Performance Complementary TFSOI BiCMOS Technology with Excellent Cross-talk Isolation and High Q Inductors for Low Power Wireless Applications," 2000 IEEE International SOI Conference , October 2000, pp. 142-143.

8. T. Stanley, "Revenue Sensitivity to Yield and Starting Wafer Cost in SOI SRAM Production," 1993 Electrochemical Proceeding of the 2nd International Symposium on Semiconductor Wafer Bonding: Science, Technology and Application , December 1993, pp. 303-309.

9. E. Leobandung, et al., "Scalability of SOI Technology into 0.13 mm 1.2 V CMOS Generation" 1998 IEEE Electron Device Meeting (IEDM) , December 1998, pp. 403-406.

10. C. Patrick Yue, et al., "A Physical Model for Planar Spiral Inductors on Silicon," 1996 IEEE Electron Device Meeting (IEDM) , December 1996, pp. 155-158.

11. A.O. Adan, et al., "Linearity and Low Noise Performance of SOIMOSFETs for RF Applications," 2000 IEEE International SOI Conference , October 2000, pp. 30-31.

12. J.G. Fiorenza, et al., "RF Power Performance of LDMOSFETs on SOI: An Experimental Comparison with Bulk Si LDMOSFETs," 2001 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium , May 2001, pp. 43-46.

13. Honeywell HRF-ROC09325 Specification Sheet, May 2001.

Jerry Yue currently leads the commercial IC and sensor technology group at Honeywell's Solid State Electronics Center, developing RF SOI CMOS, magnetic and pressure sensor product for commercial applications. He has more than 10 years of experience in SOI technology development, production transfer and yield enhancement. He has broad experience in silicon technology including bipolar, BiCMOS, high temperature SOI, SOI pressure sensor and thin-film magnetoresistive sensor. Yue holds a MSEE degree from the University of Wisconsin at Madison, holds 10 US patents and has more than 20 publications/conference presentations to his credit.

Jeff Kriz currently leads the commercial electronics wireless design group for Honeywell's Solid State Electronics Center, developing silicon-on-insulator and bulk CMOS Si MMICs. Previously, as the RF and wireless section manager at Honeywell's Technology Center, Kriz was responsible for system and component research spanning RF, microwave and mmWave applications. Prior to joining Honeywell in 1986, he worked for Texas Instruments developing GaAs MMICs. Kriz holds a MSEE degree from Southern Methodist University and a BSEE degree from the University of Illinois.