Technical Feature

Planar EM Simulation of Multi-chip Modules and BGA Packages

Jim DeLap

Agilent EEsof EDA

Westlake Village, CA

As electronics vendors and consumers demand smaller and lower cost products, manufacturers must find ways to increase levels of integration while maintaining product functionality. These higher levels of integration are often achieved by combining multiple chips onto a common substrate with a single set of inputs and outputs, hence the term multi-chip module (MCM). Multiple chips in the same module almost always require more input/output (I/O) pins; therefore, ball grid array (BGA) mounting techniques were developed to accommodate the additional connections. These packaging methods are very well understood and utilized at frequencies below 1 GHz; however, when devices need to operate at much higher frequencies, implementation of these technologies is not straightforward. The electromagnetic (EM) effects of vias, transmission lines and the I/O interface become very important and difficult to analyze.

MCM and BGA Technology

MCMs are a type of package where multiple chips, similar or different, are mounted on the same substrate. The common substrate provides multiple layers for signal and power distribution, ground connections, and interconnection of common inputs and outputs. A simple example of a multi-chip module is a RAM SIMM or DIMM commonly used in computers. These modules have multiple RAM chips mounted on the same board, utilizing a common set of I/O lines. This process not only saves board real estate, but also integrates a single function onto one board.

As the number of I/Os for the chips on this module increased, newer methods of attachment needed to be developed. Original IC packaging had a single IC bonded to a lead frame with pins along the outer edge. As ICs and packages required more and more pins, it was impractical to route signals to the outer edge of the IC. Engineers originally came up with the pin grid array (PGA), a rectangular array of vertical pins that allowed a much higher density of interconnects than standard SIMMs, DIMMs or DIPs. As frequencies of clock signals crept higher and higher, the pins ultimately presented much too high an inductance to be useful. The BGA was then developed, using solder reflow technology to attach all of the balls in a single process. The balls have a property that allows them to match the sometimes disparate thermal coefficient of expansion between the MCM substrate material, usually a ceramic, and the mounting board material.

Simulation of MCM Circuits

For the analysis of these packages, one must realize that they are essentially planar in their physical shape and construction. They can be characterized as planar sheets of dielectric material with circuit traces and vias routed on, between and through the dielectrics. Planar EM simulators exploit this nature to simplify the analysis of the electric currents.

Many tools are currently on the market for the analysis of these packages; however, many of them do not accurately predict the complete interaction between traces, vias and interconnects. Many of them simply analyze traces using a two-dimensional cross-section solver that analyzes the stackup of dielectric layers and calculates transmission line impedance along a critical network in a multi-layer structure. This method is usually a quasi-static approximation of Maxwell's equations that is typically used at lower frequencies where the physical size of the circuit is small compared to a wavelength.

For a more complete analysis of larger circuits, at higher frequencies (or both), other methods are used. The most common is the method of moments (MoM). This type of EM simulator is often referred to as a two and a half dimension (2.5D) engine. The extra half dimension means that the engine can calculate currents in the z direction (usually vias) as well as the x and y directions.

Basically, a MoM simulator includes two elements: the dielectric layer stackup and the physical layout of the traces. The dielectric stackup is how the various dielectric layers are arranged, with their respective permittivities, to simulate a cross-section of the circuit or package to be analyzed. The circuit definition is completed by adding the metallization layers, including metal conductivity and thickness, to the substrate structure.

The physical layout of the traces may be drawn using a simulator's layout capability, or imported into the layout window from a variety of formats such as DXF or GDSII. Most simulation tools include import capabilities for these and other common drawing formats. The entire purpose of drawing or importing these traces is to describe the metallization patterns of the circuit. In some analysis tools, there is also a step that maps the polygons that describe the trace metallizations to the physical location of the metals in the substrate stackup.

Once these elements that define the simulation problem are entered into the tool, the layout can be discretized for calculation of currents and S-parameters. It should be noted that since these tools implement a full-wave solution to Maxwell's equations, they include calculations for radiation effects, dielectric loss and metallization loss. These are crucial to the high frequency simulation of these packages.

It should also be noted that planar tools are not the only solutions for the analysis of these circuits. There are other tools that incorporate the full three-dimensional aspect of the problem by breaking up the volume of the model into 3D elements, applying boundary conditions and solving Maxwell's equations for the electric field. These methods are very time consuming, both for the creation of the model and extensive computation requirements. For most applications, a planar MoM solver is more than adequate. For extremely high frequencies, millimeter-wave and up, these 3D solvers might be required, but the technology of MCMs and BGA packages has not quite reached that level.

Examples

For MCMs and BGAs, the important elements of the simulation are the dielectric stackup definition and the description of a 3D structure in two dimensions. The examples shown in this article are simulated using DuPont low temperature co-fired ceramic (LTCC) material systems,1 unless otherwise noted. The ceramic is the standard Green Tape 951, while the metal systems simulated are Au 5731 for internal and buried metallizations.

The first example illustrates a common problem in MCMs utilizing LTCC materials. Since the multiple layers of ceramic are fired with metals between them, there are adhesion problems. Some ceramic layers do not completely bond to the metal layers, preferring to bond to the similar ceramic in adjacent layers. While this problem is diminishing, some vendors of LTCC systems recommend or require the use of meshed ground and power planes. This means that the metal plane separating two ceramic layers cannot be solid, or have 100 percent coverage. DuPont typically recommends 70 percent maximum coverage.

|

|

|

|

|

Fig. 1 Simulation model for a microstrip line over a solid ground plane. |

Fig. 2 Simulation model for a microstrip line over a mesh ground plane. |

Fig. 3 Simulation results for the solid and mesh ground planes. |

The use of mesh ground planes presents several problems for high frequency applications. The first is simply increased resistive losses for the ground currents when the layer is used as an RF ground. This obviously results in higher transmission line losses. The second problem is not as obvious, and is the result of the finite size of the mesh openings and the period at which they repeat. These physical factors can cause the grid to act as a filter, and are referred to as photonic bandgap structures.2,3 From Radisic, et al.2 and the parameters of this example, the frequency of this phenomenon is in the 50 GHz range, which can be neglected in most cases. The simulated models for the solid versus meshed ground planes are shown in Figures 1 and 2 , while the results from the simulations are shown in Figure 3 . The 2D layout of the mesh ground plane geometry is shown in Figure 4 to provide some insight as to how structures are drawn in a layout environment.

|

|

|

Fig. 4 Two-dimensional layout of the mesh ground plane showing the microstrip line position relative to the grid structure. |

The dielectric stackup of this simple example consists of air for the upper boundary of the line, strip metallization on top of ceramic as the substrate dielectric. The bottom boundary is a ground plane previously defined. All the MCM examples described in this article consist of variations of this definition.

One note should be made regarding the simulation stimulus of these examples. In theory, if a solid ground plane is used, it is defined in the stackup and the substrate functions are calculated assuming that the ground reference of the stimulus is an infinite, homogeneous ground plane. In the case of the mesh ground plane, an alternative ground reference needs to be used. In most simulators, if a ground is not explicitly defined, then the reference is assumed to be a sphere of infinite radius. In the case of the simulator used in these examples, a ground reference port explicitly defines the ground state. This technique is also used in the next example where the ground plane separates one mode of propagation from another in the transition from microstrip to stripline.

|

|

|

|

Fig. 5 Three-dimensional view of one method of routing a transmission line past a component in a multi-layer structure. |

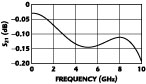

Fig. 6 S21 simulation results for the transmission line displayed in Figure 5. |

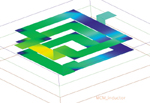

The next structure analyzed shows how transmission lines can be routed under or around active devices. This example shows a microstrip line on the top dielectric layer with a plated-through via hole creating the transition to a stripline on a buried layer, then back up to microstrip. A 3D view of the structure is shown in Figure 5 and the S-parameter simulation can be seen in Figure 6 .

Since the vias transition through a solid ground plane, there must be openings, or "anti-pads," to prevent shorting to ground. Design guidelines for the substrate materials will limit the minimum size of these via hole openings, which are 50 mils minimum in the DuPont system. The basis of this guideline is that there is shrinkage in the dielectric and metal tapes in the firing process (12.7 percent in the x and y directions for the 951 system). This could cause vias to short to ground if adequate clearance holes are not included.

Another design consideration when using vias is the number of layers through which the vias travel. If there are vias that extend all the way through the substrate, and are attached to signal lines, care must be taken that they do not act like open or short circuit stubs. This is especially true for very thick substrates with many layers. Fortunately, the LTCC processes have the flexibility to produce vias that extend only through the necessary layers. This is not always the case with traditional PCB processes.

|

|

|

|

|

|

Fig. 7 Layout for an MCM inductor. |

Fig. 8 Simulation results for the inductor. |

Fig. 9 Layout of an MCM capacitor. |

Fig. 10 Simulation results for the capacitor. |

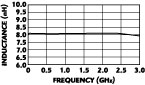

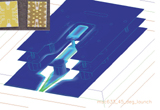

Other structures can be designed and simulated using these planar EM simulators. One advantage of the MCM methodology and LTCC implementation is the ability to incorporate passive components. The next two examples show the simulations of a 3D inductor and a parallel-plate capacitor. The inductor is created in three dimensions, using the multi-layer media to reduce the xy periphery for the same inductance. Integral capacitors can be used for device matching, AC coupling, or even lumped element filters. The inductor model is shown in Figure 7 with results displayed in Figure 8 , while the capacitor structure and simulation are shown in Figures 9 and 10 .

When considering the use of LTCC or any other substrate media, the advantages are clear. Multiple chips can be easily integrated on the surface of the substrate, while signal routing and power/ground distribution can occur on buried layers. Passive elements can also be incorporated for attenuation, matching or tuning. The only problem is that they may (and probably will) behave unexpectedly at microwave frequencies unless they are accurately analyzed using a planar EM simulator.

BGA Simulation

The next area to consider in simulating these types of packages is how they will be mounted onto a board or substrate. In many cases, the BGA attachment method is used. The ball attachment method can vary, but usually balls are soldered or brazed onto the package. The balls can vary in size and pitch, but the smaller the ball, the higher in frequency the package can operate.

|

|

|

|

Fig. 11 A microwave BGA soldered connection model with a typical BGA substrate shown in the inset. |

Fig. 12 Comparison of simulated and measured insertion loss of a BGA soldered connection. |

The main assumption when simulating BGAs is that a solder fillet will create a cylinder when the package is mounted onto a board. Since most of these EM tools can simulate vias, the ball junction can be approximated with a cylindrical shaped via. For RF signals, one technique to minimize radiation problems and confine electric currents is to surround the high frequency signal connection with ground balls. In effect, this creates a pseudo-coaxial transition.

An example of a typical microwave BGA is shown in Figure 11 , using an alumina package from Micro Substrate Corp. (model 1MSC633Z) designed to operate up to 31.5 GHz for the input and output transitions. The package also contains eight DC ports. The BGA interconnect is the most important aspect of this package at high frequencies because the path length from the die to the mounting substrate adds appreciable inductance that can ruin the frequency response of the mounted IC. For simplicity, only the RF transition was analyzed, with the measured and simulated results shown in Figure 12 .

The final example shows how these tools can also be used to simulate bond wires to chips mounted on the top layer of the substrate. A 3D view of the example is shown in Figure 13 . This is a 96-pin BGA package with an IC mounted on top. Two layers above the substrate are created to define the dielectric of the area surrounding the IC and the area surrounding the bond wires. The bond wires were created by assuming a vertical via section from the IC pad across a horizontal trace out to the bond pad, and a vertical via down to the bond pad. This method of simulating wirebonds, while not precisely modeling the three-dimensional loop characteristics, does a good job of approximating wirebonds to about 20 GHz. The results of the crosstalk simulation between two adjacent pins of the package are shown in Figure 14 .

|

|

|

|

Fig. 13 Simulation model of a 96-pin BGA with bond wires to a chip mounted on top of the substrate. |

Fig. 14 Simulation results for insertion loss of a bond wire connection and crosstalk between adjacent connections. |

Conclusion

As packaging densities and frequencies of operation each get higher, it is essential that electromagnetic effects be considered. Planar simulation tools provide a valid method for simulating these circuits without requiring the intensive computations and effort that full three-dimensional solvers require. The simulations in this article were performed using the Advanced Design System 2001's 2.5D MoM solver, Momentum, from Agilent EEsof EDA. For more information on BGA design or to download the ADS 2001 design file used in this article visit: http://www.agilent.com/eesof-eda.

Acknowledgments

The author would like to thank Bob Griffin of Micro Substrates Corp., along with Joe Civello and Chris Mueth of Agilent Technologies.

References

1. Information regarding this process and the material parameters can be obtained from DuPont's website: www.dupont.com/mcm/.

2. V. Radisic, Y. Qian, R. Coccioli and T. Itoh, "Novel 2D Photonic Bandgap Structure for Microstrip Lines," IEEE Microwave and Guided Wave Letters , Vol. 8, No. 2, February 1998, pp. 69-71.

3. D. Maystre, "Electromagnetic Study of Photonic Band Gaps," Pure Applied Optics , Vol. 3, No. 6, November 1994, pp. 975-993.

Jim DeLap is an applications engineer for Agilent EEsof EDA. He has worked in the microwave and RF community for over 13 years, and has a master's degree from the University of Virginia. He has specialized in high frequency and millimeter-wave IC and module design with further emphasis on EM effects on ICs and packages.