Unlike conduction and convection, which are linear with temperature difference, radiation has a quartic dependence on absolute temperature. Because the Stefan-Boltzmann constant is small, radiation is negligible at temperatures typically seen on Earth. In space, however, radiation becomes the only viable option as an ultimate heat sink. Therefore, the hot radiator surface temperature TH becomes the major determining factor in heat transfer capability per unit area in space, due to the quartic dependence in an otherwise low temperature, cold sky. Taking best case conditions at perfect emissivity ε = 1 and cold sky temperature TC = 3 K, the radiative cooling flux q˙rad can be plotted against hot surface temperature TH.

Most GaN devices have recommended maximum operating temperatures of about 250°C (523 K). As seen in Figure 1, even at power densities of current devices, ~50 W/cm2, the power density of GaN SSPAs is far higher than the heat transfer capability of radiative techniques. This makes the required radiator area for a given SSPA much larger than the device footprint area, and often heat management tradeoffs such as low duty cycle operation, onboard thermal storage and other indirect thermal pathways must be employed to keep the equilibrium temperature low.

It is therefore paramount to optimize the heat pathway from where the heat is being generated (microscopic hot spots on the die) to where it is ultimately rejected (the large area surface of the radiator). As power densities increase, temperatures on the die spike to very high local values, requiring high capability thermal management techniques to effectively transfer the heat to the radiator, which may be over a meter away. Minimizing the thermal resistance between the die and the radiator is what facilitates high-power density devices maintaining safe temperatures for high performance and long lifetime.

CONDUCTIVE HEAT SPREADING APPROACH

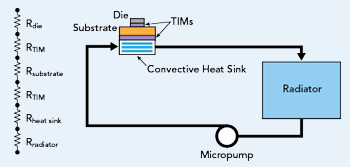

The standard method of removing heat from PAs on space payloads relies on heat spreading via conduction. The PA die is attached to a heat spreader substrate with a matched coefficient of thermal expansion (CTE) via a thermal interface material (TIM), often a solder. This substrate is then attached to a large radiator via a second TIM, often a filler paste or epoxy. This thermal stackup is shown in Figure 2. As described previously, the radiator’s surface area needs to be much larger than that of the die footprint. Therefore, there needs to be a method of connecting the die to the radiator in order to spread the heat out.

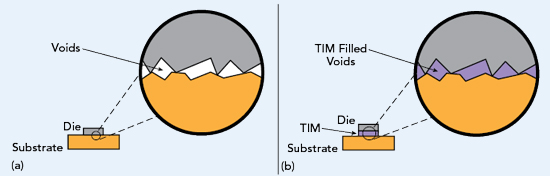

The most direct thermal pathway would be to attach the die directly to the radiator. The first issue is that, when attempting to mate surfaces, numerous voids are introduced due to the inherent roughness of each surface at the microscale. These voids cause reduced contact area between the surfaces and result in an insulating layer, thereby inducing a large resistance for heat to flow. To remedy this, thermal interface materials are applied when mating two surfaces. The goal with TIMs is to fill those voids with a thermally conductive material to minimize the resistance for heat to flow from one surface to the next, as shown in Figure 3.

Figure 3 Illustration of microscale roughness of adjoining surfaces, resulting in voids causing poor heat transmission between surfaces (a). TIMs are applied to fill in the gaps with a conductive intermediate layer, improving the thermal contact (b).

Attaching the die to the radiator via a TIM would be the next most direct thermal pathway. However, for the radiator to maximize heat rejection to the cold sky, it is ideally made of a high thermal conductivity material (aluminum, copper, etc.) to ensure a high surface temperature over the entirety of its area. Unfortunately, these high thermal conductivity materials often have large values for their CTE, introducing a mismatch with the lower CTE die. This will introduce high stress to the die and/or TIM, especially under conditions of thermal cycling seen from diurnal variations in space.

Therefore, the final solution is to attach the die to a CTE matched substrate via a first TIM, and subsequently, attach the substrate to the radiator via a second TIM. The substrate ideally has the highest thermal conductivity possible while matching the CTE of the die, which is typically a tradeoff as most CTE-matched substrate materials (Molybdenum, Tungsten, etc.) have low thermal conductivities. These substrates are made thicker to sustain stresses induced from the CTE mismatch to the high conductivity radiator, thereby relieving stress on the die while also offering some heat spreading as an intermediate step before the high conductivity radiator. Thermal conductivity and CTE values of common materials in the stackup are shown in Table 1.

The drawbacks of this robust solution include three additional thermal resistances: one from the CTE matched substrate and two from the TIMs. The resistance of the substrate is not usually problematic - it is a relatively high thermal conductivity metal material, employed in a manageable thickness. This typically adds a modest thermal resistance and may even help with initial heat spreading from the die. There are also promising new materials such as aluminum diamond and silver diamond which can be used (thermal conductivities up to 5 to 8 W/cm-K and CTE ~7.5 ppm/K) for even further reduction in resistance through the substrate.4

The TIMs, however, often become a bottleneck. Even though TIMs allow much improved conduction between surfaces compared to voids, in general, they are not very conductive. Most TIMs operate around 0.05 W/cm-K, which is a significant drop compared to the substrate and radiator materials over 2 W/cm-K. Even with attempts to enhance the conductivity of TIMs by adding complex metal microbeads or other high conductivity nanoparticles, it is rare to see filler based TIMs exceed 0.1 W/cm-K.

The thermal resistance of a TIM per unit area can be quantified based on its thermal conductivity and thickness. Taking a TIM thickness near 0.1 mm and thermal conductivity near 0.1 W/cm-K:

Therefore, for a 50 W/cm2 die, there is a ~5 K temperature jump across each TIM layer (depending on TIM type and level of spreading in the substrate). This results in needing yet a larger radiator, as the rejection temperature of the radiator cannot match the actual device temperature due to the intermediate resistances. At such power levels, a drop on the order of 10 K through the TIMs is salvageable. However, with upcoming power densities near 1500 W/cm2, a drop > 100 K across each TIM layer will be prohibitive.

In addition to the baseline heat transfer limitations at ideal conditions, there are a number of practical considerations which can make working with TIMs challenging. There are a variety of different types of TIMs applied in various circumstances depending on the application, including solders, low melting point alloys, structured carbons and various fillers (pastes, epoxies, adhesives). A few of the common challenges are listed below, some of which are more relevant to certain TIM types than others:5

- The interfacial contact resistance between the TIM and the substrate at the molecular level can add additional resistance beyond conduction through the bulk TIM. For example, carbon nanotube (CNT) TIMs have high thermal conductivity and good mechanical compliance, but often suffer from contact resistances at their interfaces with the adjacent substrates. Conceptually, this is similar to the voids that occur when no TIM is used, but at the molecular level.

- Some TIMs are challenging to integrate into the thermal stackup. Special tools, multi-step application procedures, high temperature/vacuum application conditions and long cure times are examples of things that may be required to achieve the TIM’s rated performance.

- Even with perfect application, many TIMs experience outgassing/oxidation, causing dry out and degradation over time. This results in the performance of the electronic device faltering over its lifetime, likely experiencing premature failure. There is preliminary research underway to add nanoscale coatings of higher stability compounds to prevent degradation; this may help mitigate the longevity concerns but may result in tradeoffs regarding cost and reduced bulk conductivity.

- Complex verification techniques must often be employed to ensure the TIM was applied properly. Because uniform coverage of the TIM over the entire footprint area with no voids is critical to the TIM’s functionality, advanced inspection hardware such as scanning acoustic microscopes are necessary to confirm the quality of each TIM layer in mission critical applications.

Short of TIMs that can match the thermal conductivity of the metals they bind, the conduction approach for heat spreading is starting to fall behind the capability of the devices to which they are being applied. A different technique will be necessary to support devices coming on the near horizon.

DIRECT DIE CONVECTIVE COOLING

In seeking alternatives for conduction-based heat spreading methods, convection-based approaches may be promising candidates due to their high cooling capabilities. In terrestrial systems, a variety of convective approaches are employed, such as air natural convection, forced air convection, forced liquid convection and two-phase convection. Given the long desired operational lifetimes and the lack of a surrounding atmosphere in space, closed loop liquid convection approaches are the most likely candidates. Convective cooling flux q˙conv is prescribed as:

Figure 4 Semi-log plot showing achievable convective cooling fluxes from standard liquid convection methods.

Figure 5 Standard convective cooling implementation. The convective heat sink is not integrated at the die level and therefore suffers from the same TIM issues as conductive heat spreading approaches.

Figure 6 Direct die-attach cooling methodology, integrated with ultra-high cooling effectiveness microconvective cooling including a zoomed 3D cross section of the die level cooling approach shown at the top.

In this equation, TS is the temperature of the surface in contact with the coolant, TF is the fluid coolant temperature, and h is the heat transfer coefficient, which denotes the cooling flux per degree of temperature difference achievable by a given cooling technique (W/cm2-K). Therefore, the convective cooling flux, q˙conv, is linearly proportional to the difference in temperature of the heated surface and the fluid coolant temperature. While in radiative cooling the cold sky is near 3 K, the fluid temperature cannot be taken to be as low in the convective case due to freezing considerations and the inherent thermal resistance of the radiator. Figure 4 displays what cooling fluxes can be achieved for various common liquid cooling techniques over a range of practical surface-fluid temperature differences (TS − TF).

The plot shows convective cooling fluxes up to 500 W/cm2 which appears promising for higher power density devices. However, an important distinction must be made as to the applicability of these cooling fluxes. Typical implementations of closed loop liquid cooling are not holistically different from the stackup shown in Figure 2, for the same reasons of CTE match and high conductivity heat sink requirements. TIMs are still applied between the die and the substrate, and further from the substrate onto a convective cooling module. That is, even if liquid cooling methods can match the power density of a device, they often cannot be integrated into the system without using thermal interface materials and suffer from the same thermal resistances as shown in Figure 5.

However, new methods of applying convection can change the paradigm of the thermal stackup altogether. A unique, new thermal interface concept is via direct die-attach, where the cooling module is configured such that the fluid impacts the die directly. In this methodology, fluid is brought directly to the die surface, which eliminates the TIMs and heat spreader substrates from the thermal pathway. To perform this task, the convective cooling method has two major requirements:

- It must be integrable with the die such that no intermediate affixing or spreading surfaces are required in its integration or operation.

- In order to cool devices without a heat spreader to expand the area, the convective cooling flux must match or exceed the power density of the device itself.

An emerging method called microconvective cooling by JETCOOL Technologies Inc. appears poised to meet these two requirements for cooling advanced GaN SSPAs in space. Microconvective cooling utilizes high momentum microscale fluid jets that impinge upon the heated die surface, causing strong thermal boundary layer suppression and resulting in high heat transfer capability.

This method has produced heat transfer coefficients over 40 W/cm2-K, which at a 200 K surface to fluid temperature difference, achieves convective cooling fluxes over 8000 W/cm2. The direct die-attach methodology with microconvective cooling has been successfully implemented and experimentally demonstrated cooling devices with power densities over 5000 W/cm2 in radar-based applications.6 A schematic of the thermal stackup for this new technique is shown in Figure 6. By directly bringing the fluid in contact with a passivated die surface, multiple TIM layers and heat spreaders can be removed from the thermal stackup, greatly reducing thermal resistance to the radiator in high-power density applications.

As an additional benefit, because the fluid is now directly contacting the die, the cooling module does not need to be made of a thermally conductive material. Therefore, the cooling module can be a closely matched CTE material, removing the tradeoff between thermal conductivity and CTE mismatch. Further, although the die-attach needs to be robust, it no longer needs to be perfect, as was the case in applying thermal interface materials. The thermal performance of the direct die-attach method is unaffected by the quality of the die-attach, meaning the die-attach method can focus on a strong, robust attachment mechanism instead of a high quality workmanship solution requiring high thermal conductivity, minimal thicknesses and complete, void free coverage.

Of course, the ultimate heat sink will still be via radiation to the cold sky, so there needs to be a fluid loop containing a pump and method of exchanging heat from the fluid to the radiator. Because the radiative cooling flux limitations still apply regardless of the thermal interface method, a large area radiator will still be required to reject the heat on the radiator side.

Continually advancing developments in 3D printing can be leveraged to produce optimal radiator designs containing integral cooling channels, allowing seamless integration of fluid cooling loops into the radiator workflow at low size, weight and power (SWaP). As the die level heat rejection has been decoupled from the radiator, this methodology is fully compatible with thermal storage strategies and fits seamlessly with different duty cycles and temperature cycling, with minimal control and input power requirements.

SUMMARY

With increasing power densities made possible via advanced semiconductor materials, adequate thermal management of devices is becoming increasingly challenging. The traditional method of cooling electronic devices via heat spreading through thermal interface materials and high conductivity heat spreaders is quickly reaching its limits. By employing direct die-attach cooling methodologies with high capability convective techniques, significant reductions in thermal resistance from the die to the radiator can keep devices at safe temperatures. One potential technique involving direct die-attach microconvective cooling via high velocity fluid jets shows promise as an enabling technique to facilitate devices with long lifetimes and low weight, enabling future cost-effective and highly capable space-based missions.

References

- J. Y. Tsao et al., “Ultrawide‐Bandgap Semiconductors: Research Opportunities and Challenges,” Advanced Electronic Materials, Vol. 4, No. 1, January 2018, Article No. 1600501.

- M. LaMarche, “GaN SSPA Technology for Space-Based Applications,” Microwave Journal, Vol. 62, No. 4, April 2019, pp. 20–28.

- P. D. T. O’connor, “Arrhenius and Electronics Reliability,” Quality and Reliability Engineering International, Vol. 5, No. 4, 1989, pp. 255–255.

- R. S. Pengelly et al., “A Review of GaN on SiC High Electron-Mobility Power Transistors and MMICs,” IEEE Transactions on Microwave Theory and Techniques, Vol. 60, No. 6, 2012, pp. 1764–1783.

- K. M. Razeeb et al., “Present and Future Thermal Interface Materials for Electronic Devices,” International Materials Reviews, Vol. 63, No. 1, 2018, pp. 1–21.

- S. M. Walsh et al., “Embedded Microjets for Thermal Management of High Power-Density Electronic Devices,” IEEE Transactions on Components, Packaging and Manufacturing Technology, Vol. 9, No. 2, 2018, pp. 269–278.