With the evolution of mobile services from 2G to 4G, progressively more complex signal modulation schemes have been introduced to fulfill the ever increasing data capabilities. Broader bandwidths and higher peak-to-average power ratios (PAPR) demands have had a direct impact on RF PA designs, as shown in Figure 1. From the 2G Global System for Mobile Communications (GSM) to current 4G LTE-A systems, increasing transmission rates have evolved up to 100 Mbps in the downlink and up to 50 Mbps in the uplink resulting in the need for advanced modulation techniques. The problem is how to achieve high efficiency over a broad bandwidth to decrease power consumption while maintaining linearity to ensure modulation accuracy and minimize spectral regrowth.

Figure 1 The technology development of the RF PAs with the increased PAPR of signal for wireless communication standards evolution (reprinted with permission from Artech House).1

Figure 2 Block diagram of classical envelope tracking power amplifier with analog envelope generation scheme and RF delay for branch timing (reprinted with permission from Artech House).1

This article takes a look at some of the high efficiency PA design techniques and compares their advantages and disadvantages. Several industry design experts from leading companies contributed articles on each technique: Nokia – Envelope Tracking (including Multi-Nested ET), Freescale – Asymmetric Doherty, NXP –Chireix Outphasing and Cree/Eta – Envelope Tracking/Outphasing Hybrid (Asymmetric Multilevel Outphasing).

Envelope Tracking Power Amplifier Design

The ET approach is one recommended power supply technique that maximizes the energy efficiency of the PA by keeping it in compression over the whole modulation cycle, instead of just at the peaks, by dynamically adjusting the supply voltage to the RF PA. The ET technique can be understood as a simplification of the envelope elimination and restoration (EE&R) technique.2 Rather than take out both the phase modulation (PM) and amplitude modulation (AM) information into separate paths, only the envelope AM information is extracted. Therefore, the RF PA operates in the linear region and its supply voltage altered according to the AM information. However, the supply voltage needs to be varied with adequate headroom to reduce distortion to the minimum possible amount. With the headroom available, carrying out an ET PA could be achieved without the tremendous effort as an EE&R counterpart since the ET timing matching is not as critical as that in EE&R. The block diagram and principle of an ET PA are presented in Figure 2.

Figure 3 Influence of signal statistics on time-averaging efficiency of an ET PA by comparison of PDF histogram and ET single tone efficiency trajectory over various drain supply voltage levels (reprinted with permission from Artech House).1

Figure 4 Time-domain current and voltage waveforms observed at package plane (a) and load lines of the Class P PA up to the third harmonic (b) (reprinted with permission from Artech House).1

Statistical average efficiency is an indicator for average power consumption in most wireless communication systems with time-varying envelopes. The principle behind ET is to operate the PA in the compression region as frequently as possible. This technique takes advantage of the statistic that both the point of peak efficiency and the point of peak output power vary as the supply voltage ranges between ups and downs. Figure 3 shows the drain efficiency trajectory as a function of output power for a group of supply voltage values. The output power of peak efficiency increases with a rise of supply voltages, but has a constant high efficiency across a wide output power range to tolerate back-offs for high PAPR signal probability density function (PDF) distribution. For that reason, the straightforward impression of ET is to map instantaneous output power to an optimal supply voltage value. In this manner, the PA is on the edge of the compression region most of the time. The theoretical efficiency using ET for a particular PA is presented in Figure 4 as the dashed thick black trace. As illustrated, the effective drain efficiency is substantially superior to the actual drain efficiency of a fixed supply voltage.

Envelope Generation

One of the critical aspects of ET PA design is firstly stripping the RF carrier off to reveal the envelope and then transferring it with appropriate scaling to the supply bias of RF PA in real-time manner. There are mainly two methods to realize the envelope generation. One is utilizing the RF envelope detector analog circuitry. The other is digitizing the waveform of the signal and performing a mathematical fit to determine the exact envelope values in baseband processing.

For the interfacing between envelope source and supply modulator, there are specifications to guarantee the signal integrity. For example, The Mobile Industry Processor Interface (MIPI®) Alliance, an international organization that develops interface specifications for mobile and mobile-influenced industries, has a standard analog reference interface specification between generator and supply modulator for ET called eTrakSM.1 eTrak is a multi-source vendor, independent interface that provides interoperability between the envelope generator and ET supply modulator, enabling wide deployment of ET technology in the industry. eTrak is unique in that unlike other MIPI specifications, it provides a full analog interface rather than only a port physical layer (PHY).

RF Power Amplifier Design for ET

In ET PA design, the link between the supply modulator and RF PA should be examined carefully in order to maximize efficiency and linearity systematically. Unlike small signal amplifiers that operate in the linear region, the RF PA operates in the large-signal regime, where the voltage and current pass through the entire active region of the transistor, and sometimes fall into cut-off and saturation regions. The strong nonlinearities of the RF PA result in the phenomenon of intermodulation distortion, wherein the spectral content at integer multiples of the stimulus appears at both the input and output. The linearity and efficiency performance of the RF PA is established only when these individual mixing products are handled properly.

Figure 5 Nested supply modulator with controlled current source array, which can be seen as another variant of combined hybrid topology with continuous serial hybrid and multi-current-source parallel hybrid in conjunction (reprinted with permission from Artech House).1

Even with all the advantages of the reduced conduction angle, the main problem of such PAs lies in the fact that it involves an increase in the input RF signal with the reduction in the conduction angle if the peak current is to be maintained constantly. As a consequence, the gains of such PAs are reduced, which limits the usefulness of these techniques in the design of PAs with devices possessing high gain. An alternative solution to enhancing peak efficiency while overcoming the problems caused by harmonics present in the output of the PA is to provide drain current and voltage engineered shaping for achieving Class- F, Class-F−1, Class-J and Class-P operation modes, in order to obtain increased output power and peak drain ef?ciency for ET. The Class-P design has been introduced in reference 1, as shown in Figure 4.

To alleviate the negative effects of ET, several design methods from supply modulator, RF PA and digital front end algorithms have been introduced to enhance ET techniques for wireless communication applications. Although linearity and efficiency are mutually exclusive properties in traditional fixed supplied RF PAs, ET PAs can linearly amplify amplitude and phase modulated signals with much higher efficiency. Both linear PAs and high efficiency switch mode PAs can benefit from ET with modern predistortion schemes.

Nested and Multi-Nested Envelope Tracking

For a wideband operation of the parallel hybrid supply modulator, the switching frequency of the buck switcher should be very high, leading to deterioration of the efficiency of the switcher from switching losses. This switching operation efficiency may be too high to efficiently provide the power for high PAPR signals having a broad bandwidth. In addition, to compensate for the switching ripple current, the bandwidth of the linear modulator must cover the switching frequency so that it consumes a large amount of DC power, a further deterioration in the overall efficiency.

To preserve the benefits of the combined hybrid supply modulator for higher efficiency, a further new variant of ET is the nested supply modulator. As a similar concept to the combined hybrid in Figure 5, the nested supply modulator combines the nested structure and controlled current source array technology to generate at least three points of maximum efficiency of the supply modulator in theory. In this way, the modulator can tolerate more power back-offs in handling PDF peak, which is always in motion to the low output power region and maintains high average efficiency over a wide range of power and bandwidth.

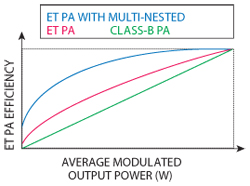

Figure 6 RF PA efficiency compared to an average modulated output–the multi-nested solution provides more tolerance to average power again (reprinted with permission from Artech House).1

The envelope voltage shaping functions are not effective for the efficiency enhancement. However, the envelope current shaping can be effective for efficiency improvement of the supply modulator. Therefore, the controlled current source array in the nested supply modulator, with envelope input control with shaping functions as efficiency is optimized to enable envelope current shaping, coordinates with envelope voltage shaping to further enhance the efficiency of the supply modulator as well as linearity optimization.

By means of this scheme combined “fast and slow” envelope tracking, the instantaneous supply voltages to RF PA drain/collector are not only correlated with instantaneous envelope shape, but also the average power of long term RF levels. Therefore, the back-off efficiency boosting capability of envelope tracking is further enhanced to wide dynamic range. It can be employed to realize highly efficient power amplification over a flexible power saving mode in LTE-A application scenarios.

Therefore, the most significant feature of a multi-nested supply modulator is to realize fast ET combined with slow average power tracking (APT) simultaneously. It further boosts the average efficiency of high PAPR signal amplification with even average output power back-off scenarios as shown in Figure 6. The slow mode APT is introduced to adjust average output power according to wireless traffic profile change as a slow way of ET to compensate the efficiency drop by adjusting overall supply voltages with traffic profile shape. Therefore, besides tracking the instantaneous envelope signal, the change of average RF power envelope can also be tracked, which determines the dynamic range parameter in the RF transmitter system and creates another dimensional capability for ET rather than the conventional fast ET only. By adding another dimension of envelope tracking, the average back-off efficiency can be extended.

Measurement Results

Figure 7 Block diagram of the multi-nested supply modulator with ideal current source array.

The schematic of this proposed envelope tracking system is shown in Figure 7. The power amplifier at 2140 MHz in reference 3 was tested with W-CDMA 10 MHz, two carrier, PAPR=6.5 dB; the proposed modulator with first and second order nested structures were implemented on the 120 W GaAs transistor with LTE 20 MHz, one carrier, PAPR clipped into 6.6 dB.

From the sweeping test results in Figure 8, higher instantaneous efficiency and back-off efficiency were observed, especially when 2nd order nested structure was applied. Approaching 63 percent collector efficiency at 58 W average output power was observed, without any linearization; greater than 45 percent collector efficiency was observed from 5 to 58 W average output power range. The average saturated output power of the transistor was increased close to 2 dB when collector modulation was implemented. However, due to Doherty utilizing two transistors, the overall saturated output power of ET PA was still lower.

As shown in Figure 4, the ET PA with and without multi-nested scheme was tested and compared. 100, 40 and 11 percent of full power was defined as the metric of wide dynamic range for enhanced LTE power saving scheme. There was no advantage when multi-nested was running in full power. However, the efficiency could be boosted by 13.3 and 24.8 percent when compared to the scenario when only single nested was implemented. These results showed benefits for wide dynamic range during power saving mode. And the concept of the proposed multi-nested was verified by this test scheme.

Figure 8 Collector efficiency comparison between Doherty and the proposed ET PA technology with/without 2nd nested ET scheme.

The multi-nested envelope tracking PA is proposed for wide average power dynamic range, which can keep high efficiency during large average output power back-offs. Principally, the PA supply is varied based on the monitored envelope levels and changed all the time so as to correctly meet the output power level of the PA at each moment of time to achieve high efficiency.

References

- Z.C. Wang, Envelope Tracking Power Amplifier for Wireless Communications, Norwood, MA, Artech House, 2014.

- S.C. Cripps, RF Power Amplifiers for Wireless Communications, Norwood, MA, Artech House, 2006.

- C. Steinbeiser, P. Page, T. Landon and G. Burgin, “Doherty Power Amplifiers Using 2nd Generation HVHBT Technology for High Efficiency Basestation Applications,” Compound Semiconductor Integrated Circuit Symposium (CSICS), 2010 IEEE, pp. 1-4, 2010.

Zhancang Wang received his bachelor’s degree in automation and master’s degree in RFIC from Beijing University of Technology in 2005 and 2008, respectively. He earned industrial experience by working in Beijing Embedded System Key Lab, RDA Microelectronics, Datang Mobile Inc., Nokia Solutions and Networks as an RFIC engineer, senior RF researcher, research project manager and consultant for 3rd party research collaborators. He focused on advanced RF technology research and prototyping, including RF transceiver architecture, linearization technology, digital front end algorithm, e.g. E-CFR, broadband and high efficiency PA technologies, e.g., Doherty and variants, envelope tracking, switch mode PA, LINC with GaN, SiC and HV-GaAs. He was an IEEE member and committee member for several international conferences. He is an author and co-author of 17 papers and six pending U.S. patents on RF PA technology.

Figure 9 Ideal two-way Doherty power amplifier.

Asymmetric Doherty Power Amplifier Design

In essence, the Doherty PA architecture utilizes dynamic loading of a Class-B amplifier. The amplifier is designed to operate into a load that is favorable to high efficiency under low RF signal levels and conversely operate into a load favorable to high power under high RF signal levels. The dynamic loading is accomplished through the synthesis of virtual loads by means of a secondary amplifier based on instantaneous output power requirements.

The Doherty PA’s implementation is relatively straightforward using standard RF matching techniques and is shown in its classical form in Figure 9. Main and peaking are tuned amplifiers typically biased in Class-B and Class-C. The two amplifiers connect to a common load through a quarterwave transmission line. At instants in time when the input signal envelope is large (thus a high output power condition), current is injected from each amplifier in-phase into load R0. At times when the input signal has low envelope levels, the peaking amplifier is disengaged and does not contribute current into the load thereby leaving only the main amplifier contributing to the output. During low envelope signal conditions, the peaking amplifier ideally acts as an open circuit.

Figure 10 Doherty power amplifier instantaneous DC-RF conversion efficiency over output power for variously sized peaking sub-amplifiers.

The quarterwave transmission line acts as an impedance inverter when high output power is required. An increasing current injected from the peaking amplifier into the common load R0, increases the effective load on the quarterwave line, Z1. This forces a reduction in the loading of the main amplifier as a consequence of the familiar quarterwave line impedance relationship of Equation 1.

With a reduced load, the main amplifier can contribute more current and therefore more power without clipping its voltage waveform – this loading effect is critical when the envelope of the signal reaches a peak.

The Doherty PA efficiency is shown in Figure 10 where significantly high efficiency is achieved over a large power range compared to a Class-B amplifier. The droop in Doherty PA efficiency is caused by the relatively low efficiency of the peaking amplifier when it contributes low output power and has low voltage swings at its output. For Doherty amplifier designs with very large peaking amplifiers, the efficiency peak is pushed to further power backoff levels, but the efficiency droop becomes excessive.

Figure 11 Idealized average Doherty power amplifier efficiency over output power for various asymmetry ratios.

Idealized average efficiency can be determined using the amplitude statistics of the signal waveform. In Figure 11, the average efficiency of various ideal Doherty PAs are plotted as a function of backoff power levels using a W-CDMA test signal waveform that is common to cellular infrastructure base stations.

At 8 dB power backoff from maximum, the idealized Doherty amplifier has an average efficiency near or greater than 50 percent. This compares to an ideal Class-B whose average efficiency is only about 27 percent. For applications where the PA operates more than about 7 or 8 dB power backoff, the Doherty amplifier with an asymmetry ratio r=1.7 achieves greater than 5 percent points higher average efficiency than the traditional symmetric Doherty of r=1.

Design Tips

Traditional RF matching techniques can be used for the input match of the main and peaking amplifiers. This includes multisection topologies. However, for broadband RF performance, the output matching networks should be designed using minimum phase networks. In addition, the main amplifier output match should be designed such that main experiences loadline modulation similar to Figure 10 as viewed at its current source plane in response to the peaking amplifier current that is modulated into the common load. In a practical Doherty design, it is possible to generate such loadline modulation by designing a singular output match based on loadpull measurements that satisfies a high efficiency load tuning with no peaking current injection, and a high power load tuning with full peaking current injection. Alternatively, if an active device model of reasonable accuracy is available, the loadline very near the main current source can be simulated and inspected in RF CAD tools during the design of the output match. Of course any charge storage on the output terminal of the active device model may displace the simulated loadline, but even this displaced loadline is usually sufficient to design the output match to ensure proper load modulation.

Figure 12 AFT18H357-24S asymmetric Doherty power amplifier pulsed CW gain and efficiency over output power.

The peaking amplifier should be designed to behave as an open circuit at the reference plane of the output combining node during low signal envelope conditions. The offset line technique used by Yang1 has proven to be an important step in practical Doherty design so as to reduce parasitic loading of the main amplifier under low envelope signal conditions. Although a comprehensive analysis of the effects of such parasitic loading has yet to be documented, particularly for broadband Doherty designs, the offset line approach is known by Doherty practitioners to improve overall amplifier efficiency.

The input signal is typically split using a 90 degree hybrid coupler. For Doherty designs with large peaking amplifiers relative to main (r > 1), it is recommended that additional power is used to drive the peaking amplifier. For example, a 5 dB directional coupler can be used for asymmetric Doherty designs in an attempt to mimic the ideal Doherty behavior shown in Figure 11. A more robust method of splitting the input signal is to use a commercially available Doherty alignment module such as Freescale’s MMDS20254HT1.2 This board level component allows for independent and dynamic digital control of amplitude and phase of each main and peaking input RF signal.

Doherty Circuit Performance

To demonstrate the performance of an asymmetric Doherty power amplifier, such a circuit was designed around a commercially available AirfastTM AFT18H357-24S packaged transistor product.3 The product represents the latest generation of silicon LDMOS device technology and was specifically designed for Doherty cellular infrastructure applications with high peak-to-average power ratios. The AFT18H357-24S peaking to main power ratio is r=1.7. The PCB measures 4 × 5 inches. The circuit can deliver over 400 W of peak output power, achieves 50 percent average efficiency at 60 W average output power, reaches over 17 dB of gain, and linearizes to stringent spectral mask requirements – all across the entire DCS downlink band (1805 to 1880 MHz). Figure 12 shows the pulsed CW gain and efficiency response as a function of output power.

Figure 13 AFT18H357-24S asymmetric Doherty two-tone video bandwidth response.

The circuit achieves excellent video bandwidth with a two-tone resonance of about 80 MHz, as shown in Figure 13. A large video bandwidth is necessary to support wide instantaneous bandwidth signals such as multicarrier GSM, LTE and W-CDMA. In addition, for Doherty PA applications where a predistorter is used for linearization, a large video bandwidth is especially important because the predistorter tends to further increase the bandwidth of the RF driving signal.

The asymmetric Doherty circuit also meets spectral mask requirements when linearized with commercially available digital predistortion systems. Figure 14 shows the linearized spectral performance of a 20 MHz wide two-carrier W-CDMA test waveform at 60 W average output power at a carrier frequency of 1843 MHz. Similar corrected performance was achieved across the DCS band.

The Doherty power amplifier provides excellent efficiency enhancement, with only marginally increased RF design complexity compared to Class-AB amplifiers. It has proven itself to be an elegant power amplifier solution in cellular infrastructure thanks, in part, to advances in digital predistortion. Asymmetric Doherty power amplifiers are now achieving 50 percent efficiency near 2 GHz with 17 dB gain for 60 W average power applications – all using cost effective silicon LDMOS device technology. It remains to be seen if an alternative amplifier architecture can ever displace Doherty’s 75 year old invention – at least in cellular infrastructure.

Figure 14 Linearized spectral performance of Freescale asymmetric Doherty power amplifier at 60 W average output power, 50 percent efficiency, fc = 1843 MHz.

Figure 15 (a) Class-E schematic with finite DC feed inductor 1 (b) Model of Class-E. Note that X is a small reactance to help maintain voltage and current orthogonality.

References

Figure 16 Efficiency as a function of normalized output power (in dB) obtained by sweeping the normalized resistance RNORM = RL/ROPT from 1 to 20 for different values of q. Best efficiency is observed for q = 1.3.

- Y. Yang et al. “Optimum Design for Linearity and Efficiency of Microwave Doherty Amplifier Using a New Load Matching Technique,” Microwave Journal, Vol. 44, No. 12, pp. 20-36, 2001.

- AirfastTM MMDS20254HT1 datasheet available at www.freescale.com.

- AirfastTM AFT18H357-24S datasheet available at www.freescale.com.

Damon Holmes received his B.Sc. and M.Sc. degrees from the University of Calgary, Canada in 2002 and 2005, respectively. He began his industrial experience at Nortel Networks, Calgary, where he was involved with the design and characterization of transceiver circuits and Doherty power amplifiers for cellular infrastructure applications. Since 2008, he has been with the RF division at Freescale Semiconductor Inc., Tempe, AZ. His research interests include MMIC design, broadband power amplifiers, high efficiency Doherty circuits and resolving power amplifier impairments. In 2013, he organized and co-authored an IMS workshop: “Tutorial on Doherty Power Amplifier Circuits & Design Methodologies.” He holds five patents awarded and pending.

Class-E Package based chireix outphasing Power Amplifier

A new approach in power device integration, matching and packaging is presented that allows designers to easily realize the benefits of Class-E in practicals designs. A new quasi load insensitive mode of Class-E that has been demonstrated to be particularly suitable for load modulation architectures.1-5

Quasi Load Insensitive (QLI) Class-E

In research circles, the Class-E PA has been popular due to its high efficiency and simple circuit structure shown in references 6, 7 and 10. In Class-E, the inductance of the RF choke is typically reduced to resonate with the device output capacitance. This is termed a ‘finite inductor’ Class- E implementation. Recent analysis on Class-E with finite bias inductor demonstrates that there exists a continuum of modes of operation which arises as the relation between load network elements and input parameters are varied as a function of the resonance factor

Figure 17 (a) Class-E switch voltage and current waveforms for q = 0 and q = 1.3 across a range of loads.

(see Figure 15) .1-5

(see Figure 15) .1-5

Among the many design solutions, there exists a unique Class-E mode of operation for q = 1.3 which yields optimum efficiency over a range of load resistances1-4 (see Figure 16). This makes it the best candidate for systems based on load-modulation such as Doherty, dynamic load modulation, or Chireix outphasing. This mode may also be advantageous where a system has to operate efficiently into an uncertain load, for example, in an RF energy delivery or microwave heating application. The conventional Class-E mode, where q → 0 with infinite inductor impedance is not ideal for load-modulation unless a more complex – and therefore more lossy – variable load network is deployed.5,8

Waveforms of current through, and voltage across, the active device as simulated using the model in Figure 15(b) are shown in Figure 17 for both the classical Class-E mode and the QLI mode. Figure 17a shows that the voltage waveform for the classical mode at nominal load resistance reaches zero at switch turn on time, a condition critical for efficiency. As the load resistance is increased, however, the voltage at the instant of switch turn-on moment increases. This has the effect of allowing simultaneous voltage drop and current flow to exist at the switch plane, and dissipation to occur. By comparison, as shown in Figure 17b the unique property of the QLI mode is that as the load resistance increases, the turn-on voltage slope changes from zero to a negative value while still maintaining the turn-on voltage close to zero.

Theory to Measurement – QLI Class-E in Package

When considering how to make use of high efficiency switching modes, the high frequency of operation of GaN makes it an ideal choice. The first design2 to make use of the QLI Class- E mode was an asymmetric combiner Chireix outphasing PA featuring bare 2.4 mm GaN dies wire bonded to the planar coupler based combiner and matching circuit. However, in standard ceramic packages, the device designer is limited by the available matching network topologies that can be practically realized. The series capacitor in particular is difficult to implement internally, so a functionally identical transformed arrangement has been derived from the Class-E network.

The Class-E in package (CEiP) has been built using NXP 0.25 um, 28 V GaN HEMT technology and commercially available NXP flanged ceramic package SOT1135A. The inductor L1 is realized inside the package using bond wires. Since the higher harmonic terminations are handled inside the package, a conventional fundamental load pull system is sufficient to obtain the optimum impedance for both maximum efficiency and maximum output power, as is shown in Figure 18. Equally useful, a conventional fundamental-only matching circuit is all that is required to achieve these high efficiency figures in practice.

Figure 18 CW 2.14 GHz load-pull data at 4 dB gain compression of CEiP device.

To prove out the design of high efficiency linear PAs using the new CEiP device technology, a mixed mode Chireix outphasing PA has been constructed for 2.1 GHz operation, as shown in Figure 19. The Chireix outphasing combiner topology and the mixed mode operation is described in reference 9.

The efficiency, output power and ACPR figures have been characterized for single and quad-carrier W-CDMA signals after linearization (see Figure 20). The CEiP outphasing PA achieves 20 W with 61 percent PAE for a single carrier W-CDMA signal with a PAR of 7.1 dB. ACPR is better than 54 dBC. For the quad-carrier (20 MHz) W-CDMA with a PAR of 9.6 dB 11 W is achieved with PAE >53 percent and ACPR close to 48 dBC which can be improved with advanced DPD.

Acknowledgment

The authors wish to acknowledge the help and support of Melina Apostolidou, Keith Finnerty, Jan Vromans, Rik Jos, Fred van Rijs, Michel de Langen, Thomas Roedle, Lex Harm, Jawad Qureshi, Jordan Svechtarov and the prototype line from NXP.

References

- M.P. van der Heijden, M. Acar and S. Maroldt, “A Package-Integrated 50 W High-Efficiency RF CMOS-GaN Class-E Power Amplifier,” 2013 IEEE MTT-S International Microwave Symposium Digest (IMS), 2013, pp. 1,3, June 2-7, 2013.

- M.P. van der Heijden, M. Acar, J.S. Vromans, and D.A. Calvillo-Cortes, “A 19 W High-Efficiency Wide-Band CMOS-GaN Class-E Chireix RF Outphasing Power Amplifier,” 2011 IEEE MTT-S International Microwave Symposium Digest (MTT), pp. 1-4, June 5-10, 2011.

- M. Acar, A.J. Annema and B. Nauta, “Generalized Analytical Design Equations for Variable Slope Class-E Power Amplifiers,” Electronics, Circuits and Systems, 2006, ICECS ‘06, 13th IEEE International Conference, pp. 431-434, December 10-13, 2006.

- D.A. Calvillo-Cortes, M.P. van der Heijden, M. Acar, M. de Langen, R. Wesson, F. van Rijs and L.C.N. de Vreede, “A Package-Integrated Chireix Outphasing RF Switch-Mode High-Power Amplifier,” IEEE Transactions on Microwave Theory and Techniques, Vol. 61, No. 10, pp. 3721-3732, October 2013.

- M. Ozen, R. Jos, C.M. Andersson, M. Acar, and C. Fager, “High-Efficiency RF Pulse Width Modulation of Class-E Power Amplifiers,” IEEE Transactions on Microwave Theory and Techniques, Vol. 59, No. 11, pp. 2931-2942, November 2011.

- N.O. Sokal and A.D. Sokal, “Class E-A New Class of High-Efficiency Tuned Single-Ended Switching Power Amplifiers,” IEEE Journal of Solid-State Circuits, Vol. 10, No. 3, pp. 168-176, June 1975.

- F.H. Raab, “Idealized Operation of the Class E Tuned Power Amplifier,” IEEE Transactions on Circuits and Systems, Vol. 24, No. 12, pp. 725-735, December 1977.

- F.H. Raab, “High-Efficiency Linear Amplification by Dynamic Load Modulation,” 2003 IEEE MTT-S International Microwave Symposium Digest, Vol. 3, pp. 1717-1720, June 8-13, 2003.

- J.H. Qureshi, M.J. Pelk, M. Marchetti, W.C.E. Neo, J.R. Gajadharsing, M.P. van der Heijden and L.C.N. De Vreede, “A 90 W Peak Power GaN Outphasing Amplifier With Optimum Input Signal Conditioning,” IEEE Transactions on Microwave Theory and Techniques, Vol. 57, No. 8, pp. 1925-1935, August 2009.

- R. Beltran and F.H. Raab et al., “An Outphasing Transmitter Using Class-E PA’s and Asymmetric Combining,” High Frequency Electronics, April 2011.

Figure 19 Circuit model of the Class-E in package (CEiP) based Chireix outphasing PA including the output matching network (a)–the input match is not shown for the sake of simplicity. Photograph of the 2.1 GHz mixed-mode Chireix outphasing power amplifier module (b).

Figure 20 Linearized ACPR for single and quad-carrier W-CDMA signals.

Asymmetric Multilevel Outphasing Power Amplifier Design

Higher efficiency PAs must be accompanied by the wider bandwidth and high linearity demands of 4G (and future) wireless signals. To address this issue, recent startup Eta Devices Inc. is commercializing a technology developed at MIT: Asymmetric Multilevel Outphasing (AMO). AMO combines the high linearity of outphasing with efficiency-enhancing, multi-level, discrete switched drain bias. Discrete switched drain biasing is the key to supporting wide bandwidths while maintaining high efficiency, and provides an advantage over traditional envelope tracking. Figure 21 illustrates how AMO achieves efficiency improvement over outphasing alone.

Figure 21 Theoretical efficiency of AMO modulation with four amplitude levels, compared to two level AMO and "one level" outphasing (or LINC – LInear amplification with Nonlinear Components).

In any outphasing system, the maximum efficiency is determined by the performance of the PAs. In its high power amplifier designs, Eta Devices uses GaN HEMT devices from Cree Inc., which have demonstrated practical peak drain efficiencies exceeding 80 percent.

AMO Operation

Two well-known methods for achieving linear amplification with nonlinear power amplifiers are outphasing and envelope tracking (ET).

Outphasing basically uses two phase modulated amplifiers operating at constant amplitude. The input signal is converted to the proper phases and presented to the amplifiers, with outputs combined so that reinforcement and cancellation of the phase components results in a signal that accurately replicates the input. In practice, outphasing requires a power combiner that provides a consistent load for each PA, isolation between the amplifiers, and high power handling capability. These characteristics can be difficult to maintain over wide bandwidth.

Envelope tracking splits the signal into separate phase angle and amplitude components. The PA operates in saturated mode, typically one of the switching modes such as Class-E, F or inverse Class-F. Phase modulation is applied to the RF drive while the drain voltage is modulated with the amplitude envelope, thus phase and amplitude are both restored at the output. ET, despite its popularity, is greatly challenged by the increasing bandwidth requirements of 4G and WLAN standards. The crux of the problem is the DC supply modulator, which must handle a lot of power, be extremely efficient, be highly linear, be high resolution, inject very little noise into the system, and support wideband modulation.

The design challenges of outphasing and ET are addressed by Asymmetric Multilevel Outphasing (AMO), which combines their most desirable features. The amplitude modulation of ET is simplified to discrete steps instead of a wide bandwidth, linear analog range. With multiple drain voltage steps, outphasing then has a series of smaller operating ranges, which maintains high PA efficiency while reducing performance demands on the power combiner.

AMO solutions do require non-traditional digital predistortion (DPD) solutions, which are at the core of Eta Devices’ intellectual property. Although non-traditional, the necessary computational resources do not differ from that of traditional DPD, thus there is no hidden cost associated with increased digital complexity.

Figure 22 The AMO test transmitter block diagram.

GaN Devices and Transmitter Design

PA performance determines the maximum system efficiency of outphasing, ET and AMO. Presently, the highest efficiency production devices are fabricated using GaN processes. For example, the Cree CGH40010 GaN HEMT devices1 used in a prototype developed at MIT2 is specified at 65 percent (3.6 GHz) and >70 percent (2 GHz) typical efficiency at its maximum saturated output power. For AMO application, the PA is designed for good performance over the range of drain voltages to be delivered by the stepped-switching supply modulator.

A complete AMO transmitter is illustrated in Figure 22. Baseband I and Q signals are delivered to a DPD and modulation signal processor implemented with a FPGA. In this evaluation system, DPD is implemented with a lookup table constructed from measured static nonlinearity of the transmitter for the various DC levels at the PA.

Outphasing channel phase modulation data is delivered to digital-to-analog converters and phase modulators for the two PAs. The stepped amplitude modulation data, with coarse delay correction, drives the supply modulator circuit. RF preamplifiers provide the necessary drive levels, and at the output a combiner sums the PA outputs into a single RF signal.

Figure 23 Efficiency versus bandwidth at 2.14 GHz, 100 W peak power, 7 dB PAPR and ACPR > 45 dBc. Supply modulator losses are included in the efficiency measurement.

Performance Summary

Combining the desired attributes of outphasing and envelope tracking achieves much higher performance than could be obtained with either method alone. Figure 23 shows efficiency versus bandwidth performance for the four-level AMO test transmitter. The advantages of the AMO system architecture using Class-E GaN PAs, combined with the latest DPD implementation, deliver an average modulated drain efficiency of 70 percent at 1 MHz bandwidth, with only a slight reduction to 68 percent at 20 MHz bandwidth.

While this transmitter has 70 percent modulated drain efficiency at maximum output power, the performance at backoff is arguably more important. This is because it is normal to operate well below the maximum average power. Eta Devices’ system only loses 10 percent of efficiency for 10 dB backoff from the maximum average power. For a signal with a 7 dB PAPR, this is actually a 17 dB backoff from peak power.

For more information on this technique, read “GaN Devices and AMO Technology Enable High Efficiency, Wide Bandwidth Wireless Transmitters” in the March 2014 issue of Microwave Journal.

References

- CGH40010 data sheet, Cree Inc., available at www.cree.com/rf/.

- P. Godoy, S.W. Chung, T. Barton, D. Perrault and J. Dawson, “A Highly Efficient 1.95 GHz, 18 W Asymmetric Multilevel Outphasing Transmitter for Wideband Applications,” IEEE International Microwave Symposium Digest, June 2012.

Raymond S. Pengelly gained his BSc. and MSc. degrees from Southampton University, England in 1969 and 1973 respectively. He worked for Plessey Co. in the UK, Tachonics Corp., Compact Software and Raytheon Commercial Electronics. Since August 1999, he has been employed by Cree Inc. in Durham, NC. Initially, he was the general manager for Cree Microwave responsible for bringing Cree’s wide bandgap transistor technology to the commercial marketplace. From September 2005 he became responsible for strategic business development of wide bandgap technologies for RF and microwave applications for Cree and most recently has been involved in the commercial release of GaN HEMT transistors and MMICs for general purpose and telecommunications applications. He has written over 120 technical papers and four technical books, holds 15 patents and is both a fellow of the IEEE and fellow of the IET.