Low temperature co-fired ceramic (LTCC) is an increasingly popular technology that has the potential for increased reliability, improved electrical performance, size reduction and reduced cost. The LTCC process allows passive components such as resistors, inductors and capacitors to be embedded in a multilayer, integrated module with high density and low cost. The design of circuits with dense, embedded passive components is nontrivial, however, due to the electromagnetic (EM) interactions causing parasitics that may lead to non-ideal circuit behavior.

A systematic procedure that incorporates electromagnetic interactions is necessary to achieve an optimal and reliable circuit design. This article illustrates a novel procedure to design passive and active modules, while including all electromagnetic effects. The designs were created using modern commercial circuit simulation tools that have integrated planar and three-dimensional electromagnetic simulators.

The article begins with an overview of LTCC, including a discussion of the advantages of LTCC solutions using modern circuit simulation. Embedded passive components modeling is highlighted with some emphasis on the model library construction process. LTCC design is illustrated using a diplexer example with simulation results compared to measurements.

LTCC Overview

LTCC is a process technology that allows RF engineers to create modules with integrated passive components. The great advantage of LTCC is that ceramic technology circuit elements such as capacitors, resistors and inductors can be implemented in a small space and at low cost. Figure 1 illustrates a typical LTCC module. Each layer is printed with metallized circuit patterns that are electrically interconnected from layer to layer by conductive vias. The individual layers are assembled, laminated under pressure and heated as a unit (co-fired) to create a monolithic structure. Highly conductive metals such as silver or gold metal alloys can be used because a low temperature is maintained during curing. Each layer is a ceramic composite with very stable dielectric properties. Active or passive devices such as RF integrated circuits (RFIC), microwave monolithic integrated circuits (MMIC) and surface-mount devices (SMD) may be placed on the surfaces.

Fig. 1 LTCC geometry using multiplelayers and allowing integrated passive structures.

Design Challenges

The goal of LTCC design is to create components with better performance, greater functionality and smaller size while reducing cost and time-to-market. Accomplishing this compound goal has the associated reality that more embedded components are required to provide that functionality. Integrated LTCC RF module design requires RF characterization of internal structures for which there are often no electrical models. Many embedded components, especially spiral inductors and parallel plate capacitors, have large areas. Parasitic coupling from such large components with other structures and/or to ground planes is often significant. The process for characterizing passive components must include parasitic effects, not only to determine their value, but also to evaluate any unintentional or intentional coupling to other structures. It is important to develop a reliable RF characterization of these coupling mechanisms to ensure a successful design. Compounding the problem is the challenge that buried components are difficult to characterize using measurements. Even with sophisticated probe station measurements, comprehensive de-embedding procedures may not properly eliminate the effect of vias, pads and probes.

LTCC Design Flow

The RF electronics industry has long been recognizing the value of EM modeling technology. Now, powerful 3D EM simulation (in this case Ansoft’s HFSS) is complemented by system, circuit and planar EM simulation in an integrated environment called Ansoft Designer.™ This product is ideal for LTCC design and development as it includes the rigorous EM simulation that is required for RF characterization and validation. Furthermore, fully parameterized libraries of components can be developed based upon results from EM simulation. Simulations can include all EM effects, including parasitic effects for closely placed devices. An entire LTCC module layout can be simulated using HFSS to model all electromagnetic coupling, thus ensuring proper device operation prior to fabrication.

Figure 2 is a flowchart describing the design flow for LTCC modules. System-level simulations are performed first to establish the architectural design and for selecting critical components. Detailed electrical circuit design follows by assembling models for components based upon a particular foundry process. The physical layout is created simultaneously with the circuit schematic because each component is described in a single database containing electrical and physical attributes. The designer can modify the physical layout and re-orient components based on layout constraints. EM-based tuning and optimization can be performed by co-simulation with planar EM or 3D HFSS simulators. A final 3D verification is then performed to include all parasitic effects and coupling between components. Any performance degradation can be compensated at this stage by adjusting the physical layout. The value of this design flow for LTCC is that validation of the results occurs only once using measurements. If properly followed, this design flow eliminates design-test-redesign cycles that have often hindered successful product development in the past. Furthermore, the integration among system, circuit, layout and EM simulation eliminates barriers between tools that previously required tedious design re-entry and lack of model compatibility between design domains.

Fig. 2 Design flowchart for LTCC modules.

Embedded Passives Modeling and Library Development

Embedded passive components, as found in LTCC structures, can be modeled effectively using EM simulation. Components such as capacitors, inductors, vias and other interconnects are the primary interest since they represent the majority of passive components used. Organizations that are incorporating LTCC into their product development process should generate a component library so that often-used components can be readily incorporated into their designs.

Scalable HFSS Models

A unique feature of the new design flow is that 3D electromagnetics is fully integrated within the circuit simulation environment. A “scalable” HFSS model is a component that can be parameterized in its dimensions, material parameters, boundary conditions and frequency. It is possible for designers to co-simulate between circuit and electromagnetic domains with all functionality such as tuning, optimization and parametric sweeps. An HFSS component model is added to a circuit schematic by inserting a sub-circuit identified as an HFSS N-port design. The interface gives the designer the option to interpolate results from an existing library of HFSS results or to simulate missing points in the parameter space. A spiral inductor, for example, may have geometric parameters including the number of turns, trace width, spacing between turns and the inner diameter. In this instance, the S-parameters versus frequency make up a four-dimensional parametric space over which circuit simulations may be performed. For physical parameters between HFSS-solved data points, the circuit simulator will perform a multi-dimensional, complex interpolation to resolve the magnitude and phase. This interpolation is fast, which makes it possible for designers to perform real-time tuning and fast circuit optimization. Once the design space has been sufficiently explored, the designer may choose to simulate between data points in the parameter space by selecting the option to simulate missing points. The HFSS solver is automatically invoked whenever the circuit simulation requests a new parametric data point.

Diplexer Example

In this section, simulation of an LTCC diplexer with embedded passive elements will be discussed, highlighting the full-wave electromagnetic field simulation. The diplexer under consideration is part of a direct conversion transceiver for GSM/DCS wireless applications made by Soshin Electric of Japan.1 The device has a low band between 810 and 960 MHz and a high band between 1710 and 1990 MHz. Fine details of the circuit and layout are proprietary, therefore some simplification of the schematic will be made for this example. The final EM validation with full-chip layout will use the actual layout of the module available from Soshin. Figure 3 depicts the diplexer schematic, including the low pass and high pass sections. As seen in the figure, there are numerous electromagnetic components including embedded capacitors, inductors and vias buried within the LTCC module. These components have traditionally been included in circuit simulations using circuit models. In that which follows, components will be simulated using full-wave 3D finite elements. The electromagnetic simulations are parameterized allowing the creation of a process-dependant library.

Fig. 3 Schematic of the diplexer with low and high pass sections.

The diplexer layout is a composite structure containing four capacitors, three spiral inductors and numerous vias. All components have circuit simulation models based on 3D HFSS electromagnetics using the scalable HFSS modeling method described above. All geometry is based on the foundry process and models are accurate to the limits of foundry repeatability.

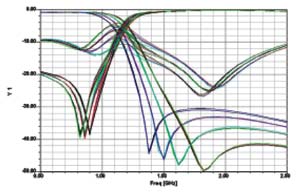

The schematic in Figure 3 can be analyzed using linear frequency-domain circuit simulation. Simulations performed using nominal dimensions resulted in a diplexer crossover frequency of 1 GHz, a low pass rejection of 34 dB and a high pass rejection of 18 dB. Figure 4 is a 3D view of the diplexer layout as modeled in HFSS. Whereas the previous simulation used EM simulation for each component in isolation, this new model simulates all elements in concert to include all coupling between components. Two capacitors used in the diplexer (circled in the figure) have been parameterized to allow tuning of the design. Parameter L1 is the width of the first shunt capacitor of the low pass and parameter L2 is the width of the second series capacitor in the high pass. L1 was swept from 0.5 to 1.1 mm in 0.2 mm steps (four instances); L2 was swept from 0.45 to 0.95 mm in 0.25 mm steps (three instances). Figure 5 is a cumulative plot of the results of the parametric sweep in HFSS. L1 was swept from 0.5 to 1.1 mm in 0.2 mm steps; L2 was swept from 0.45 to 0.95 mm in 0.25 mm steps. As can be seen in the figure, sweeping L1 has the dominant effect of reducing the low pass corner frequency and L2 has the effect of increasing the high pass corner frequency. Tuning the performance of the diplexer also can be automated using optimization.

Fig. 4 Three-dimensional HFSS model of the entire diplexer layout.

Fig. 5 Parametric sweep of the capacitor dimensions L1 and L2 tunes the filter corner frequencies.

3D Verification

As mentioned earlier, the actual circuit schematic and layout of the Soshin diplexer is proprietary and cannot be shown in this article. The simulation results and measurement results, however, can be shared. Figure 6 is an E-field plot near conducting surfaces generated by an HFSS simulation of the entire layout. In this model, all EM couplings between components are computed and included when computing the S-parameters.

Fig. 6 The HFSS simulation of the entire layout computes all EM coupling between components.

Figure 7 is a plot that compares simulated with measured results for the diplexer using an EM analysis similar to that used previously but, this time, using the actual Soshin layout. The results show that the power of modern 3D field simulation can accurately predict LTCC module performance. The remarkable agreement between simulated and measured results is a testament to the value of integrating 3D EM simulation into the LTCC design process.

Fig. 7 Comparison of simulated and measured performance of the Soshin Electric diplexer.

Conclusion

This article provided an introduction to LTCC structures and outlined a novel procedure to design LTCC modules using modern commercial software tools. An integrated design flow was illustrated, emphasizing the ability to incorporate 3D EM simulation tools upfront in the design process to reduce the build-and-test approach that has historically plagued designers of high performance LTCC systems. LTCC design was illustrated with a diplexer module example. Advantages that may be gained by coupling advanced EM field solvers with high frequency circuit simulation for LTCC design were demonstrated.